CONTROL, AUTOMATION, ROBOTICS CONFERENCE, April 22-24, 2017, Nagoya, Japan

# Neuro-Inspired Adaptive Manycore SoCs and Applications

#### Abderazek Ben Abdallah

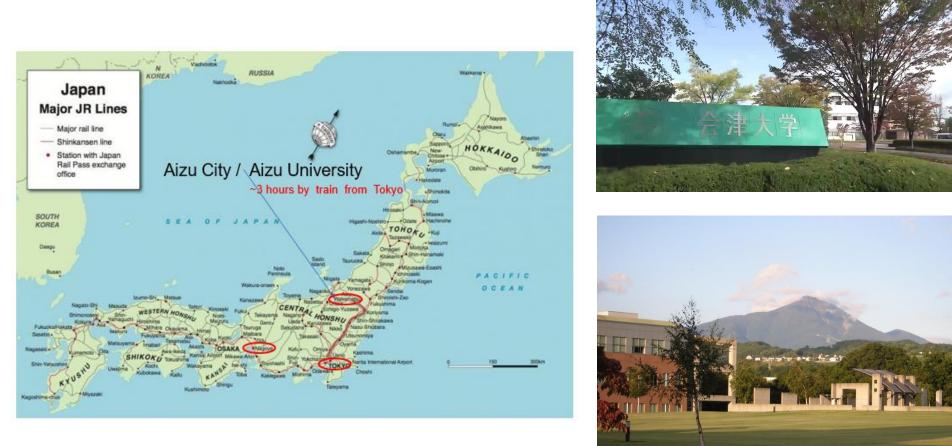

University of Aizu Division of Computer Engineering Adaptive Systems Laboratory benab@u-aizu.ac.jp

### **Aizu University**

Selected as a Top Global University by Ministry of Education, Culture, Sports, Science and Technology (MEXT)

# **Computing Trends: Opportunities & Challenges**

- Huge progress in IC technology

- Emergence of IoT, Embedded/Ubiquitous/Pervasive applications.

- Large bandwidth and low power requirements.

- Data become more knowledge intensive (unstructured).

- Performance is limited by the **Communication** Network rather than the **Computation** Logics.

## **Neural Networks**

benab@u-aizu.ac.jp

## **System-on-Chip**

Self-test

control

DSP

core

DRAM

Interface

control

Memory

array

CPU core

Legacy

core

IP hard

core

I/O pads

- Multi/Many cores integrated on a single chip:

- Technology scaling

- 3D integration

- Many examples

- STMicro

- picoChip

- Tilera Tile GX, Tile Pro <sup>soc</sup>

- Intel Polari , ...

- Complex apps, strict constraints

- Massively parallel applications

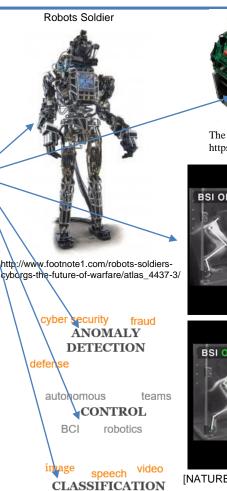

- Big-data Analysis, Pattern Recognition, Deep Learning

medical

signature

The Soccer Robot based on SoCs. https://www.intechopen.com/

[NATURE, VOL 539, 10 NOVEMBER 2016]

- **Compute** (High-performance, Real-Time)

- Adapt (needs to run in dynamic environments, where physical context, network topologies, and workloads are always changing)

- Learn (No programming!)

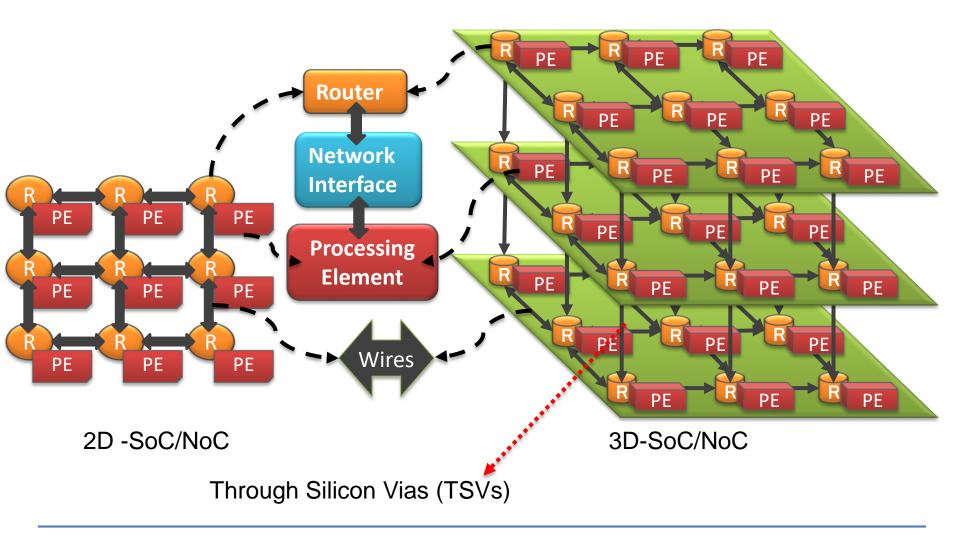

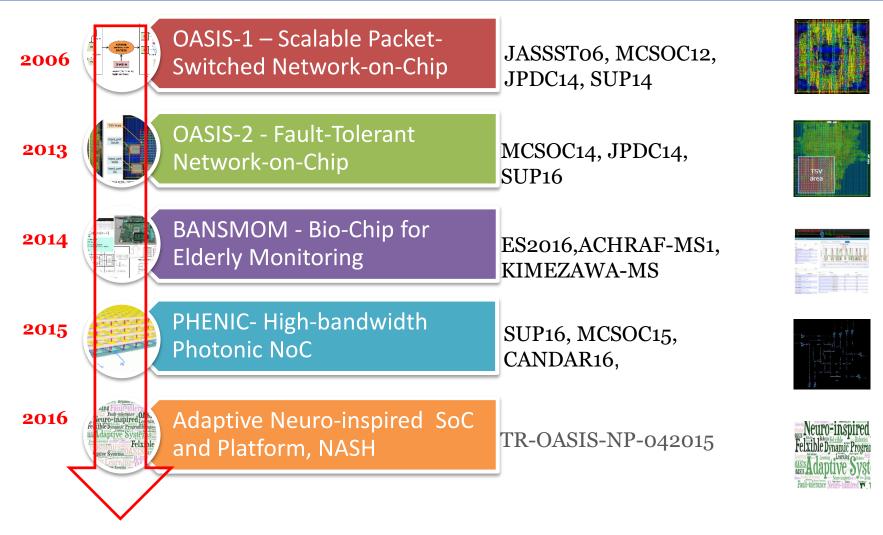

#### ASoC - Approach I: Scalable Packet-Switched SoC/NoC

#### ASL Approach I: Scalable Packet-Switched SoC/NoC

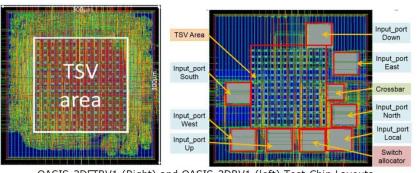

OASIS-3DFTRV1 (Right) and OASIS-3DRV1 (left) Test-Chip Layouts

- Technology: 45nm CMOS Process

- Chip Size: 2.205X2.220 (micron)

- Frequency: 0.91

GHZ Confirmed

- Supply voltage: 1.1V

- Power Dissipation: 222.387

uW

- Number of Pins: 557

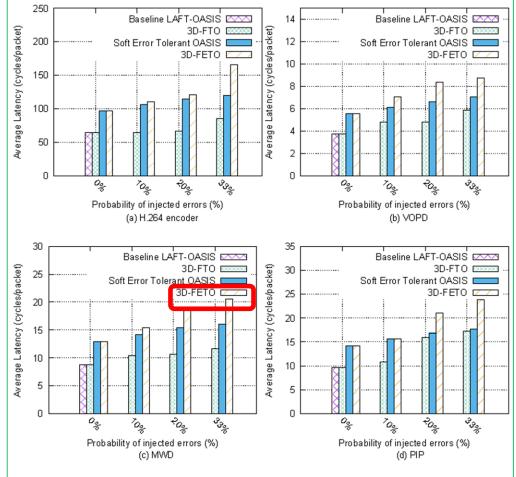

Figure 10: Average packet latency evaluation of the realistic benchmarks.

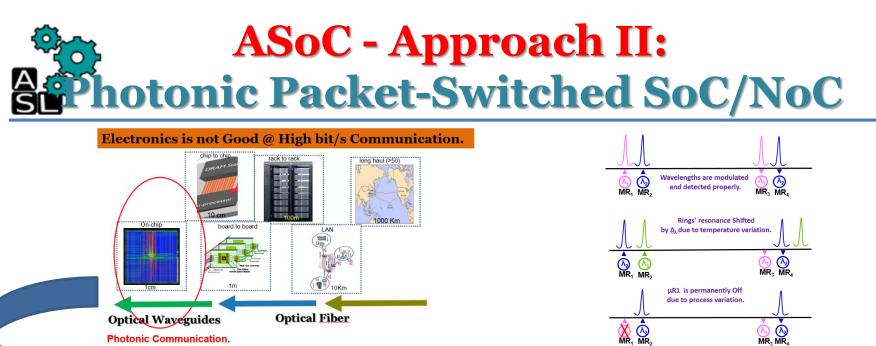

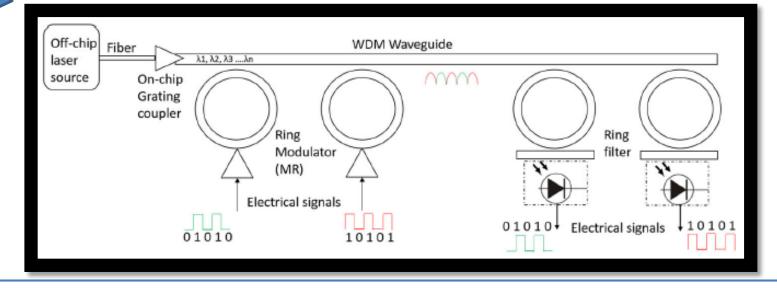

Photonic Communication.

Modulators

Detectors

benab@u-aizu.ac.jp

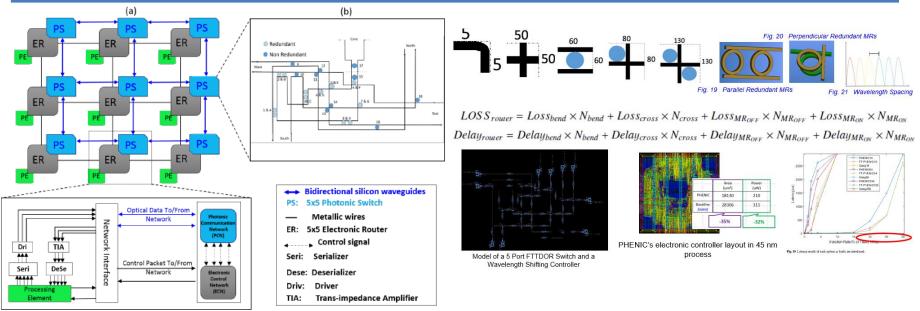

#### ASoC - Approach II: Photonic Packet-Switched SoC/NoC

- (c) (a) 3x3 Mesh-based System, (b) 5x5 non-blocking photonic switch, (c) Unified Title.

- ✤ Micoring fault-tolerant

- ✤ Can support enormous intrinsic data bandwidths.

- ✤ Immune to the electrical interference.

- ✤ Bit-rate transparency

- ✤ Transmission latency is very small Depends on the group velocity of light

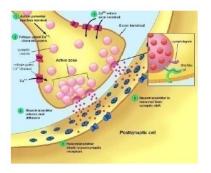

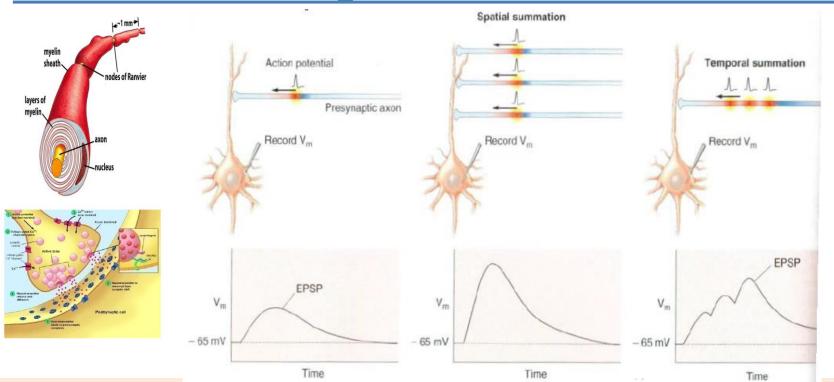

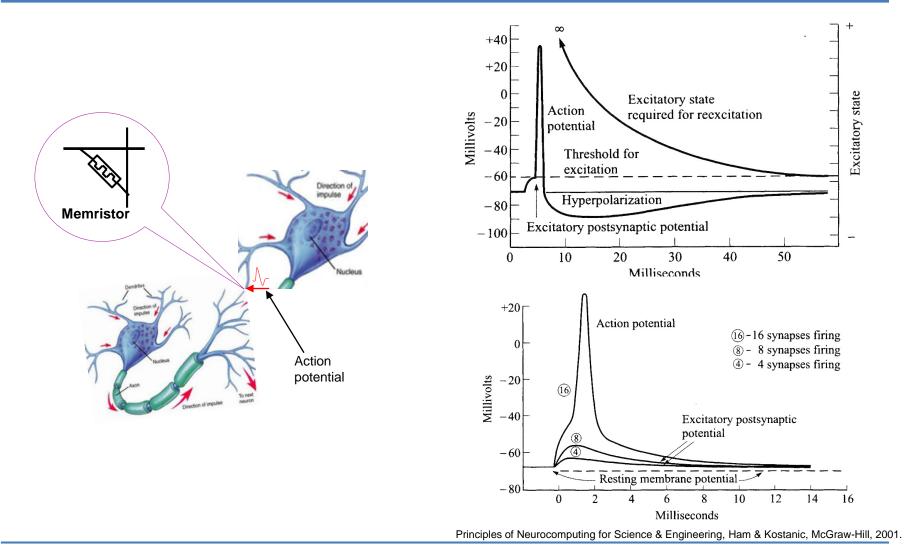

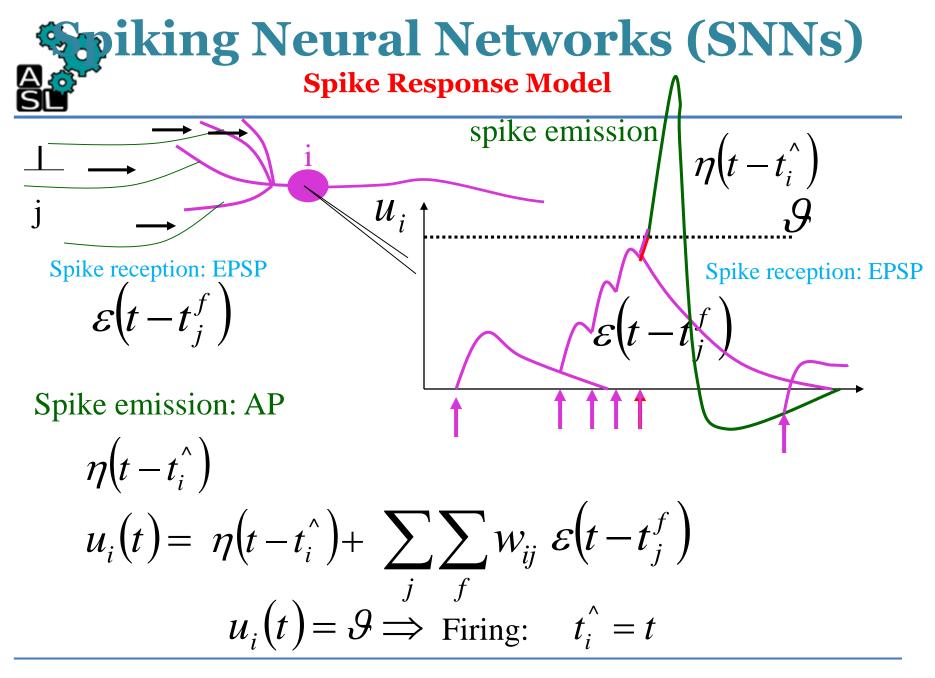

- Neurons accumulating charge and firing over periods of time.

- Different from traditional ANN models, which are static organizations of mathematic formulas.

- Adaptive, spike-based (time dependent) and its structure can change over time:

- -Neurons and synapses may be created or destroyed over time.

#### The return to the neuro-inspired computing – Why Now?

- Huge progress in IT technologies

- > Number of PCs, cell phones doubles every 5 years

- Emergence of nano-devices

- Better understanding of neural functions

- IC power consumption is reaching its limit

- Brain is extremely energy efficient  $- > \sim 10^{-16} \text{ j/op/s vs. } 10^{-16} \text{ j/op/s for the best}$

computers today [NCLJ.A.Bullinaria2015]

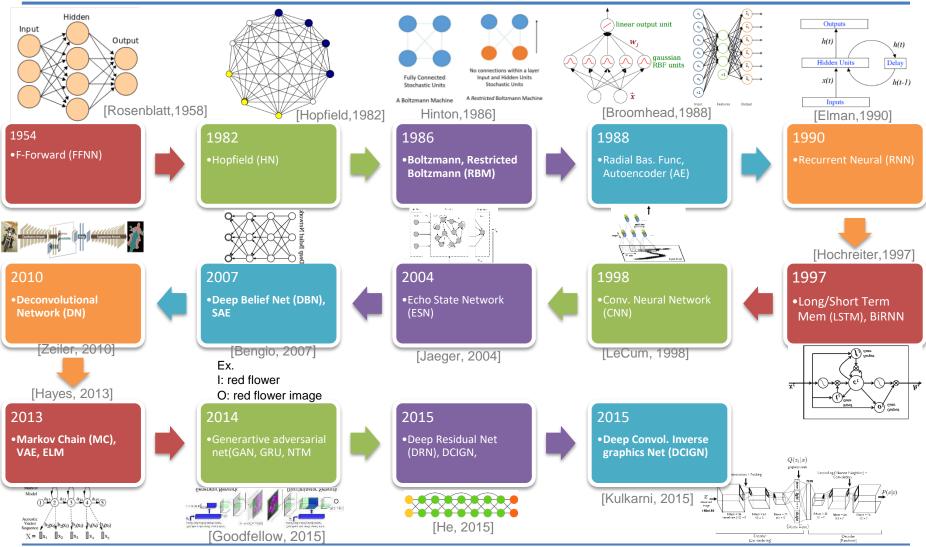

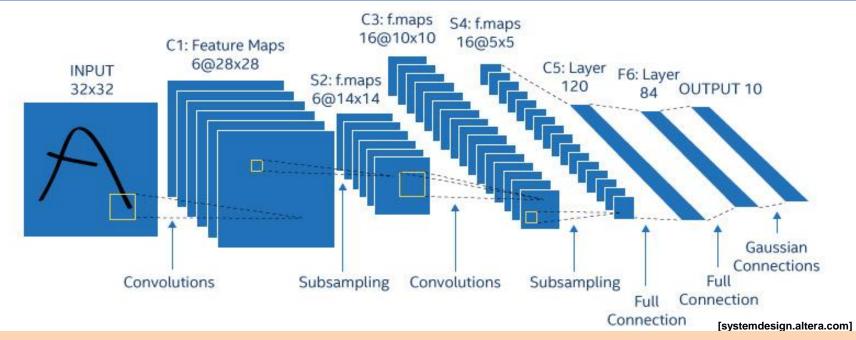

#### Deep Neural Network for DL Parallel and Deep

#### Deep Neural Network for DL Parallel and Deep

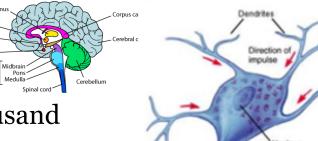

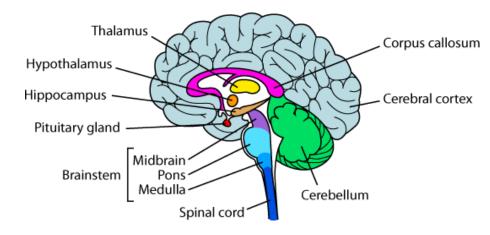

### **Brain Features**

Brainstem

- Ten billion (10<sup>10</sup>) neurons

- Neuron switching time >10<sup>-3</sup>secs

- On average, each neuron has several thousand connections

- Hundreds of operations per second

- Face Recognition ~0.1secs

- High degree of parallel computation, Distributed representations

- Each neuron is connected to the others through 10000 synapses

- It can learn, reorganize itself  $\rightarrow$  adaptive

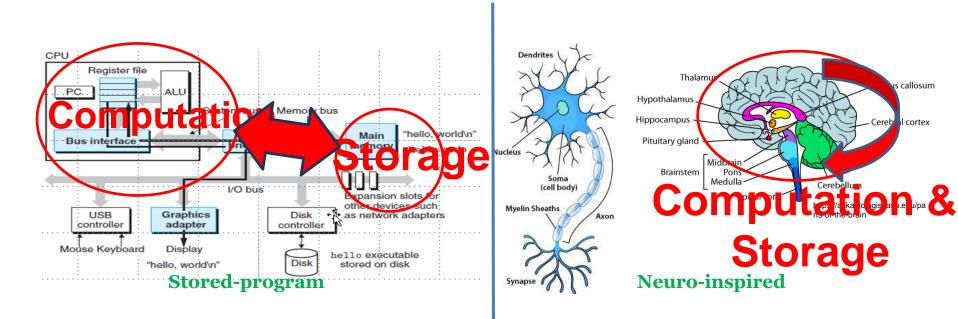

# **Computer Vs. Brain**

- Computer

- Calculation

- Precision

- Logic

#### • Brain

- Pattern Recognition

- Noise Tolerance

- Complexity

- High Power

- Storage and computation are separated

- Poor at recognition

- Low Power

- Storage and computation are not separated

- Good at recognition

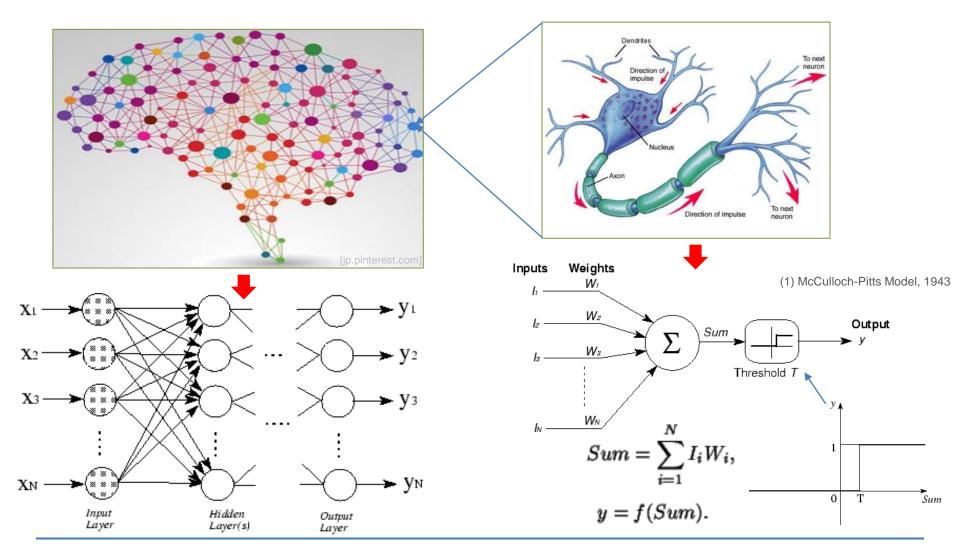

## Simplistic Neural Network Models

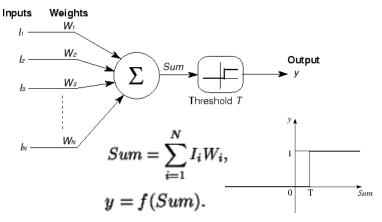

#### (1) Linear threshold gate (McCulloch-Pitts Model, 1943)

W1,W2...Wm are weights normalized in (0,1) or (-1,1), *Sum* is the weighted sum, and *T* is a threshold constant, the function f is a linear step function at threshold *T*.

This model is so simplistic that it only generates a binary output and also the weight and threshold values are fixed.

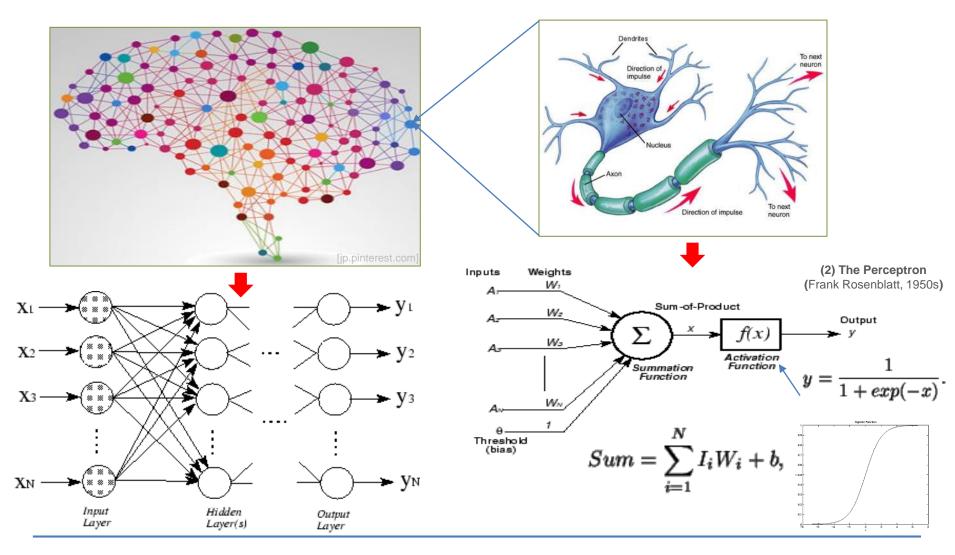

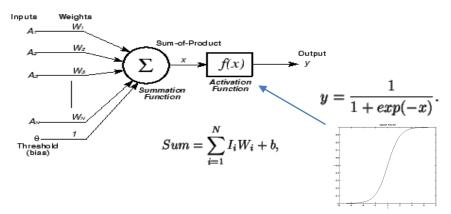

#### (2) The Perceptron (Frank Rosenblatt, 1950s)

- Merging between McCulloch-Pitts model and **Hebbian learning** rule of adjusting weights.

- In addition to the variable weight values, the perceptron model added an extra input that represents **bias**.

#### Deep Neural Network for DL Parallel and Deep

- DNN/DL systems have been highly successful in the areas of image classification and customer preference determination.

- They are not designed for applications that are timedependent/dynamic, which is our focus.

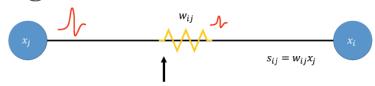

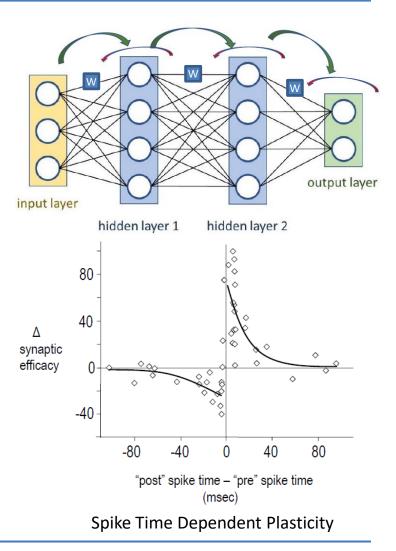

# **Spike Time Dependent Plasticity**

- Large number of highly interconnected neurons with small local memory, communicating via spike timing.

- Connections (synapses) holds knowledge (weights)

- Need **training** on examples (supervised/un-supervised learning) to adjusts weights (learning rule)

# Short term and long term plasticity for adaptive architecture

- Time multiplexing  $\rightarrow$  Dynamically reconfigurable interconnect

- Short term and long term Plasticity → Adaptive architecture

- Time/space summation → Memory/logic operations at interconnect

- Time/space synchronization  $\rightarrow$  Noise/defect tolerant signal processing

April 23, 2017

# ...but great opportunities come with great challenges

# How do we interconnect a large number of SNs in a networked many-core fashion?

# We should consider:

- Scalability

- Area utilisation

- Power consumption

- Throughput

- Synapse/neuron ratio

#### The brain is a network of neurons

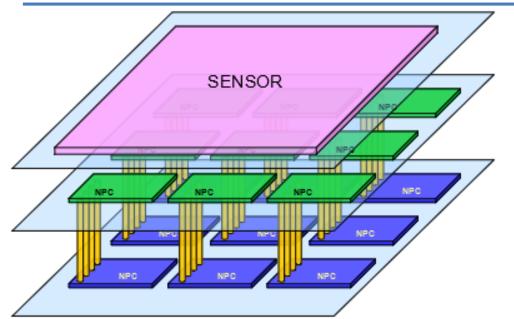

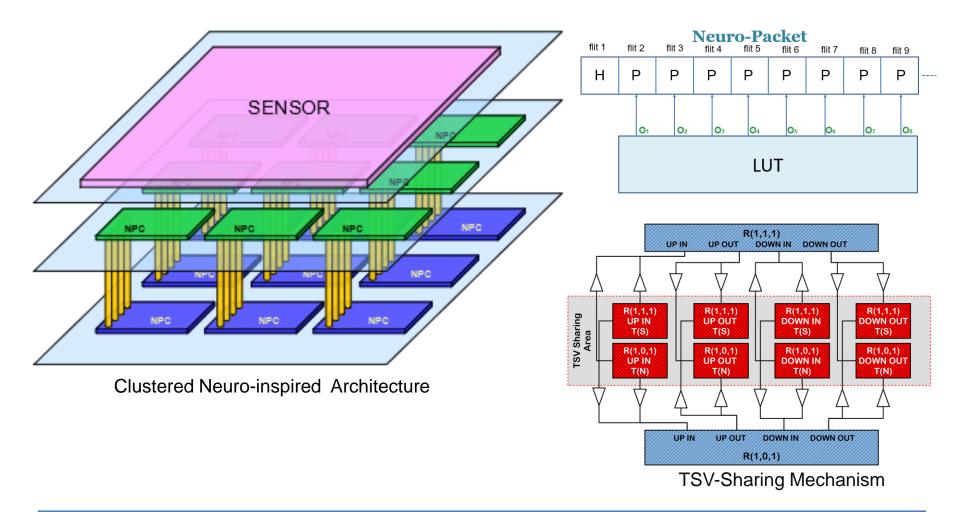

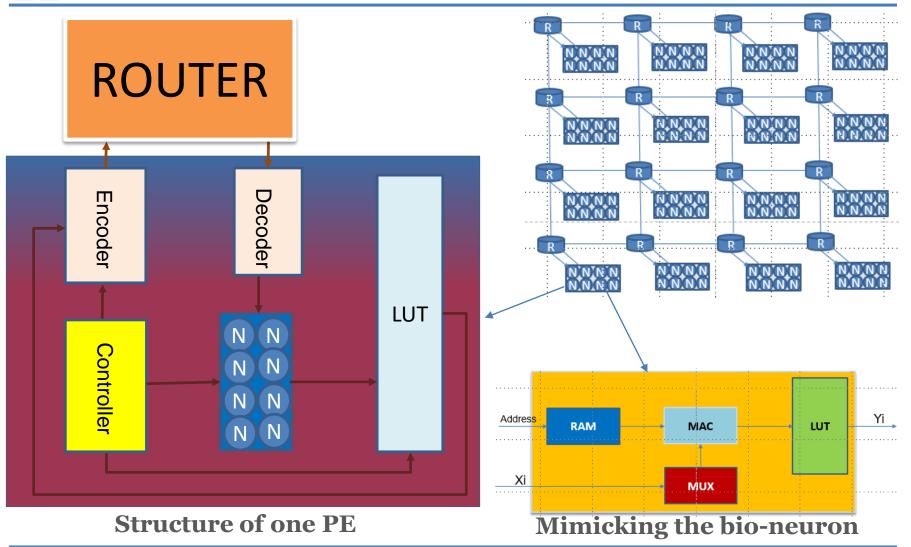

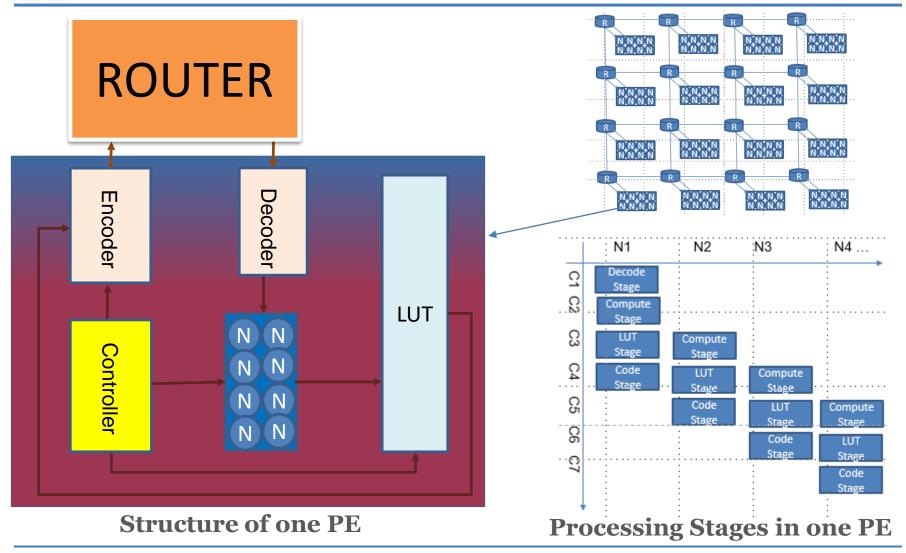

### Seuro-inspired ArchitectureS in Hardware - NASH

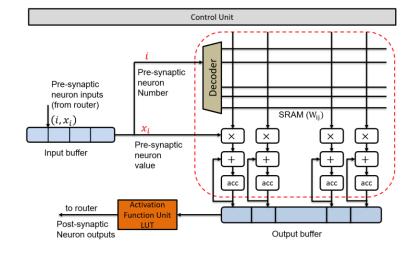

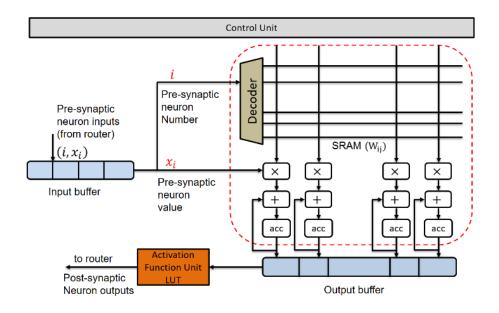

A Single NPC based on SRAM

NASH processes data coming from sensors via 3D-TSV.

Each neuro core processes a collection of N neurons each with M synaptic weights Wij.

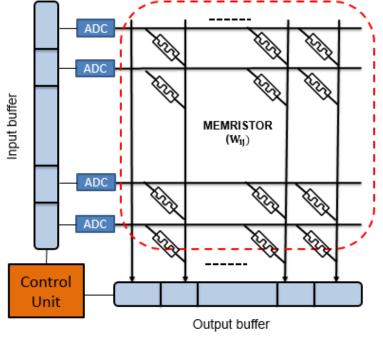

## Neuro-inspired ArchitectureS in Hardware - NASH

(a) MEMRISTOR based Neuro Processing Core (NPC)

(b) SRAM based Neuro Processing Core (NPC)

## **Neuro-inspired ArchitectureS in** Hardware - NASH

### **Neuro-inspired ArchitectureS in** Hardware - NASH

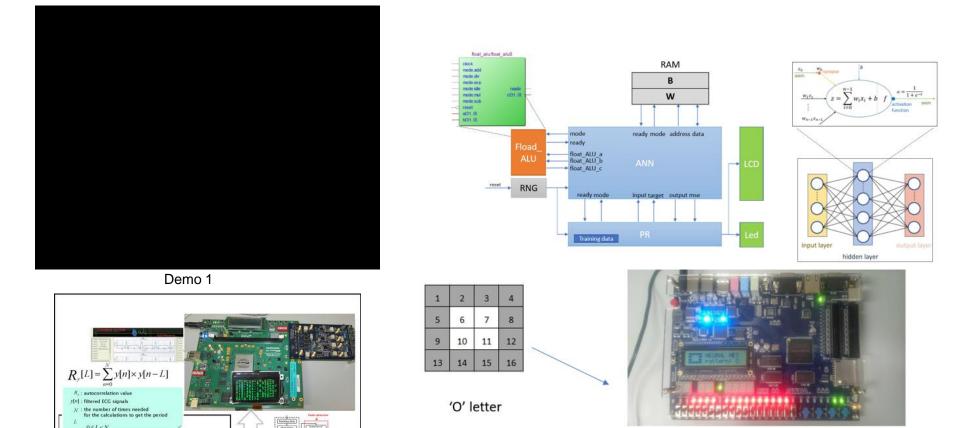

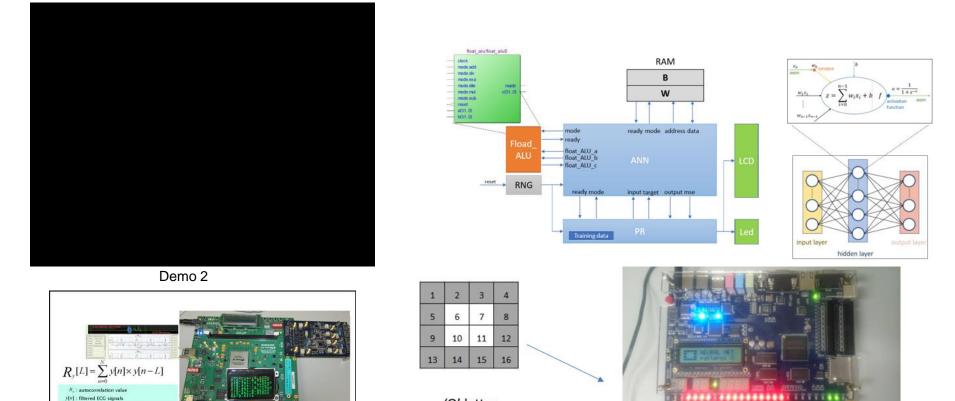

# **Some ASoC Applications**

Character Recognition based on BP training

(b) Filtering (c) Analysis (d) Display

**BANSMOM System (Conventional)**

Figure 2. BANSMOM system architecture.

(a) Signal reading

PPD Algorithm - Autocorrelation

# **Some ASoC Applications**

'O' letter

Character Recognition based on BP training

(a) Signal reading

: the number of times needed

the calculations to get the perio

Figure 2. BANSMOM system architecture.

(b) Filtering (c) Analysis (d) Display

**BANSMOM System (Conventional)**

PPD Algorithm - Autocorrelation

## **ASL Adaptive SoCs**

# Thank you!

#### Abderazek Ben Abdallah benab@u-aizu.ac.jp

#### to Advance Knowledge for Humanity