# Algorithms and Architectures for Spiking Neuromorphic Systems

## Vu Huy The

### A DISSERTATION

SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN COMPUTER SCIENCE AND ENGINEERING

Graduate Department of Computer and Information Systems

The University of Aizu

2019

COPYRIGHT BY VU HUY THE ALL RIGHTS RESERVED.

#### THE THESIS TITLED

# Algorithms and Architectures for Spiking Neuromorphic Systems

BY

## Vu Huy The

IS REVIEWED AND APPROVED BY:

Chief referee

Professor, The University of Aizu, Japan

Abderazek Ben Abdallah

Professor, The University of Aizu, Japan

Toshiaki Miyazaki

Professor, The University of Aizu, Japan

Tsuneo Tsukahara

Professor, The University of Aizu, Japan

Junji Kitamichi

Professor, Keio University, Japan

Hideharu Amano

THE UNIVERSITY OF AIZU 2019

# Contents

| 1 | Inti | RODUCT                                                  | TION                                              | 1  |  |  |

|---|------|---------------------------------------------------------|---------------------------------------------------|----|--|--|

|   | 1.1  | 1.1 Brain-inspired Computing: Towards a New Computation |                                                   |    |  |  |

|   |      | Paradi                                                  | gm                                                | 1  |  |  |

|   |      |                                                         | Von Neumann Architecture                          | 1  |  |  |

|   |      |                                                         | Brain-inspired Computing                          | 4  |  |  |

|   | 1.2  | Motiva                                                  | ation: Power, Scaling, and Reliability Challenges | 7  |  |  |

|   | 1.3  | Disser                                                  | tation Goals and Contributions                    | 10 |  |  |

|   | 1.4  | Disser                                                  | tation Organization                               | 11 |  |  |

| 2 | Neu  | iral Ne                                                 | etwork Architecture: Background                   | 15 |  |  |

|   | 2.1  | Neural                                                  | Network                                           | 16 |  |  |

|   |      |                                                         | Overview                                          | 16 |  |  |

|   |      |                                                         | Neural Network Topologies                         | 18 |  |  |

|   | 2.2  | Artific                                                 | ial Neural Network                                | 19 |  |  |

|   |      | 2.2.1                                                   | Learning Rules                                    | 19 |  |  |

|   |      |                                                         | Supervised Learning                               | 20 |  |  |

|   |      |                                                         | Unsupervised Learning                             | 20 |  |  |

|   |      | 2.2.2                                                   | Fundamental Implementation                        | 20 |  |  |

|   |      | 2.2.3                                                   | Existing Architectures                            | 22 |  |  |

|   | 2.3  | Spikin                                                  | g Neural Network                                  | 23 |  |  |

|   |      | 2.3.1                                                   | Neural Coding Methods                             | 24 |  |  |

|   |      |                                                         | Rate Coding                                       | 24 |  |  |

|   |      |                                                         | Temporal Coding (Spike coding)                    | 25 |  |  |

|   |      | 2.3.2                                                   | Neuron Models                                     | 25 |  |  |

|   |      |                                                         | Hodgkin-Huxley                                    | 26 |  |  |

|   |      |                                                         | Izhikevich                                        | 28 |  |  |

|   |      |                                                         | Leaky Integrate and fire                          | 29 |  |  |

|   |      | 2.3.3                                                   | Spiking Neural Network Learning Rules             | 30 |  |  |

|   |      |                                                         | Unsupervised Learning                             | 30 |  |  |

|   |      |                                                         | Supervised Learning                               | 31 |  |  |

|   |     | 2.3.4   | Communication Network                                              | 31 |

|---|-----|---------|--------------------------------------------------------------------|----|

|   |     | 2.3.5   | Existing Architectures                                             | 31 |

|   | 2.4 | Conclu  | asion                                                              | 33 |

| 3 | Rel | ATED W  | Vorks                                                              | 35 |

|   | 3.1 | Spikin  | g Neuromorphic Systems                                             | 35 |

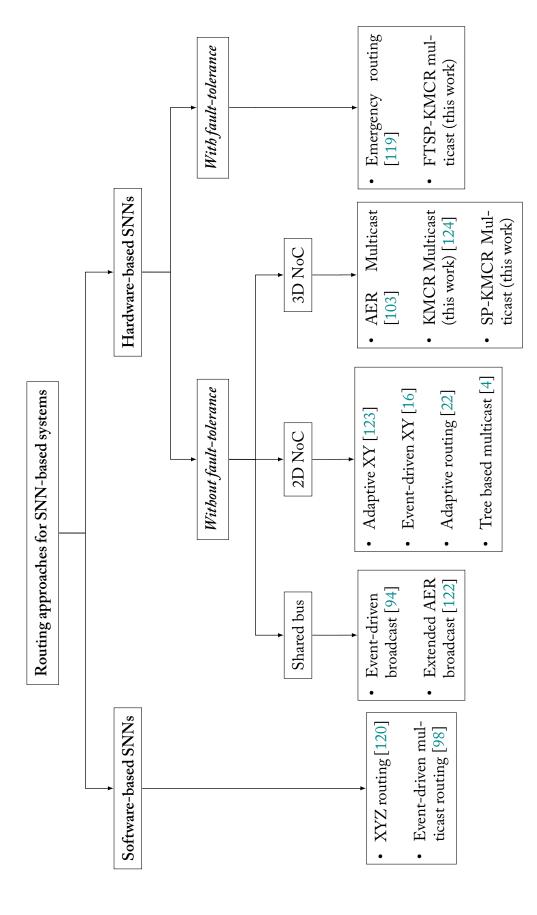

|   | 3.2 | Inter-r | neuron Communication                                               | 38 |

|   |     | 3.2.1   | Hierarchical Bus-based Spike Routing                               | 40 |

|   |     | 3.2.2   | 2D Packet-swiched-based spike routing                              | 40 |

|   |     | 3.2.3   | 3D Packet-swiched-based Spike Routing                              | 41 |

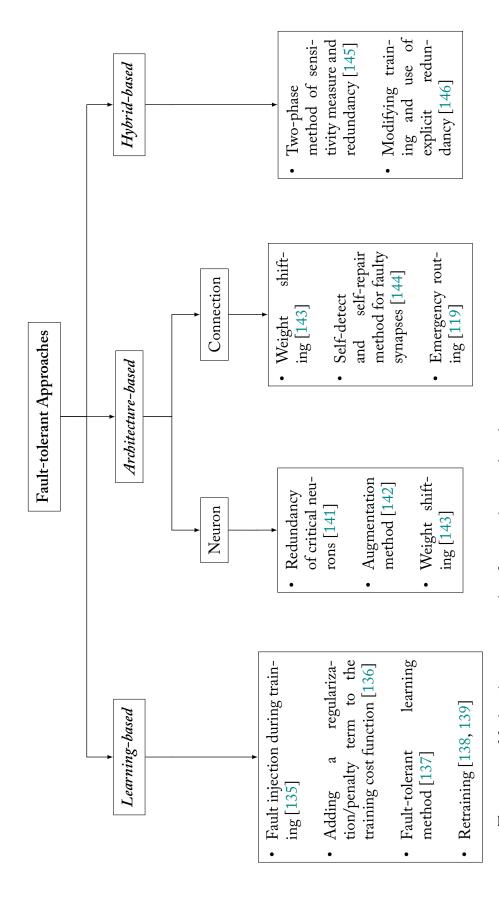

|   | 3.3 | Fault-t | olerant Neural Network                                             | 43 |

|   |     | 3.3.1   | Learning-based approaches                                          | 43 |

|   |     | 3.3.2   | Architecture-based approaches                                      | 45 |

|   |     | 3.3.3   | Hybrid approaches                                                  | 46 |

|   | 3.4 | Conclu  | asion                                                              | 47 |

| 4 | Сом | 1PREHE  | nsive Analytic Performance Assessment                              | 49 |

|   | 4.1 | Assum   | ption and Network Model                                            | 50 |

|   | 4.2 | Non-fa  | aulty System Assessment                                            | 52 |

|   |     | 4.2.1   | Performance Analysis of Hopfield NN Based on a 3D-mesh             | 52 |

|   |     |         | Unicast-based Spike Routing                                        | 52 |

|   |     |         | Multicast and Broadcast Based Routing Schemes                      | 53 |

|   |     | 4.2.2   | Performance Analysis of RNDC NN Based on a 3D-mesh                 | 55 |

|   |     |         | Unicast Based Routing                                              | 55 |

|   |     |         | Multicast Based Routing                                            | 56 |

|   |     |         | Broadcast Based Routing                                            | 57 |

|   | 4.3 | Faulty  | System Assessment                                                  | 58 |

|   |     | 4.3.1   | Performance Analysis of Hopfield Neural Network Based on a 3D-mesh | 58 |

|   |     |         | Unicast-based Spike Routing                                        | 58 |

|   |     |         | Multicast and Broadcast Based Routing Schemes                      | 60 |

|   |     | 4.3.2   | Performance Analysis of RNDC Neural Network Based on a 3D-mesh     | 61 |

|   |     |         | Unicast based Routing                                              | 61 |

|   |     |         | Multicast and Broadcast Based Routing Schemes                      | 62 |

|   | 4.4 | Conclu  | asion and Discussion                                               | 63 |

| 5 | К-м | ieans B | ased Multicast Spike Routing Algorithms                            | 65 |

|   | 5.1 | K-mea   | ns Based Multicast Spike Routing Algorithm (KMCR)                  | 66 |

|   |     | 5.1.1   | The Proposed Routing Algorithm (KMCR)                              | 66 |

|   |     | 5.1.2   | Selection of the Optimal Number of Clusters                        | 71 |

|   |     | 5 1 3   | Wedknoint                                                          | 73 |

|   | 5.2 | Shortest Path K-means Based Multicast Routing Algorithm (SP-KMCR)) 73 |                                                                        |     |  |

|---|-----|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----|--|

|   | 5.3 | Fault-to                                                              | olerant Shortest Path K-means Based Multicast Routing Algorithm (FTSP- |     |  |

|   |     | KMCR                                                                  | 3)                                                                     | 74  |  |

|   |     | 5.3.1                                                                 | Proposed Fault-tolerant Routing Algorithm                              | 74  |  |

|   |     | 5.3.2                                                                 | Fault Management Algorithm                                             | 79  |  |

|   | 5.4 | Conclu                                                                | sion                                                                   | 81  |  |

| 6 | Tow | ards Sc                                                               | calable Spiking Neuromorphic Architecture                              | 83  |  |

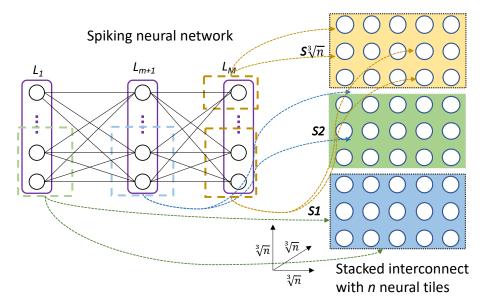

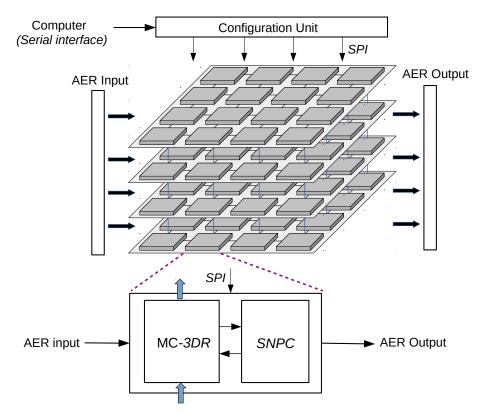

|   | 6.1 | System                                                                | Architecture                                                           | 84  |  |

|   |     | 6.1.1                                                                 | Topology                                                               | 85  |  |

|   |     | 6.1.2                                                                 | System interface                                                       | 85  |  |

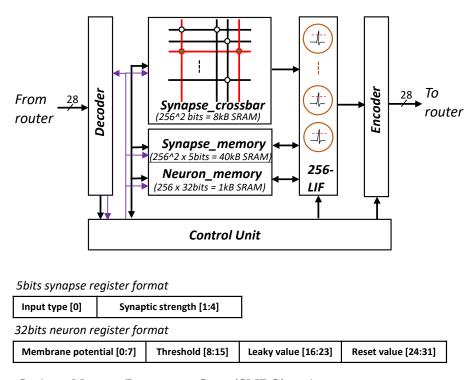

|   | 6.2 | Spiking                                                               | g Neuron Processing Core (SNPC)                                        | 86  |  |

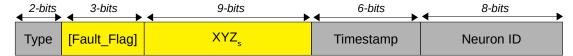

|   | 6.3 |                                                                       | packet format                                                          | 88  |  |

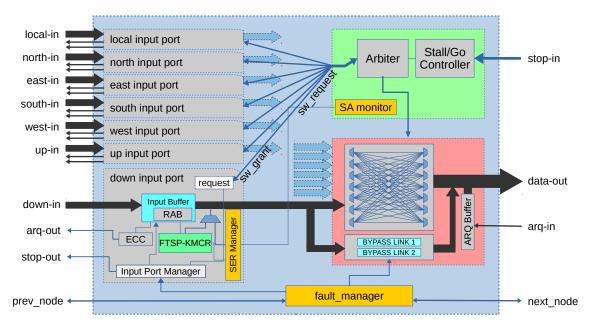

|   | 6.4 | Router                                                                | Architecture                                                           | 90  |  |

|   |     | 6.4.1                                                                 | Spike routing table                                                    | 91  |  |

|   |     | 6.4.2                                                                 | Hard fault tolerance                                                   | 92  |  |

|   |     |                                                                       | Fault-tolerant buffer                                                  | 92  |  |

|   |     |                                                                       | Fault-tolerant crossbar:                                               | 92  |  |

|   |     |                                                                       | Fault-tolerant TSV                                                     | 92  |  |

|   | 6.5 | Applica                                                               | ation deployment                                                       | 94  |  |

|   |     | 6.5.1                                                                 | Application mapping methods                                            | 94  |  |

|   |     | 6.5.2                                                                 | Input-data-to-spike conversion methods                                 | 94  |  |

|   |     |                                                                       | Converting from original data sets                                     | 96  |  |

|   |     |                                                                       | Using converters                                                       | 96  |  |

| 7 | Des | IGN AND                                                               | Evaluation                                                             | 99  |  |

|   | 7.1 | Method                                                                | dology                                                                 | 99  |  |

|   | 7.2 |                                                                       |                                                                        | 100 |  |

|   |     | 7.2.1                                                                 | Spike Injection Rate Analysis                                          | 100 |  |

|   |     | 7.2.2                                                                 | K-means Based Multicast Routing Algorithm Evaluation                   | 101 |  |

|   |     |                                                                       | Performance Evaluation Under Realistic Benchmarks                      | 101 |  |

|   |     |                                                                       |                                                                        | 107 |  |

|   |     |                                                                       | · · · · · · · · · · · · · · · · · · ·                                  | 110 |  |

|   |     | 7.2.3                                                                 | Shortest Path K-means Based Multicast Routing Algorithm Evaluation     | 112 |  |

|   |     | 7.2.4                                                                 | Fault-tolerant K-means Based Multicast Routing Algorithm Evaluation    | 119 |  |

|   |     |                                                                       | Performance Evaluation                                                 | 120 |  |

|   |     |                                                                       |                                                                        |     |  |

|   |     |                                                                       | _                                                                      | 123 |  |

| 8 | Con | CLUSION                                                               | ns and Future Work                                                     | 125 |  |

References 149

# List of Figures

| 1.1 | Computation paradigm is shifted from (a) von Neumann (centric computation) to (b) brain-inspired computing (distributed computation)                                                                                                                                                                                                                                        | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | End of the road - a shringking challenge of of physical gate length at 10nm [3]                                                                                                                                                                                                                                                                                             | 3  |

| 1.3 | Power density and clock frequency challenges of conventional computing architecture [4]                                                                                                                                                                                                                                                                                     | 3  |

| 1.4 | An illustration of ANN and SNN hardware implementations for a hand-written digit recognition application.                                                                                                                                                                                                                                                                   | 5  |

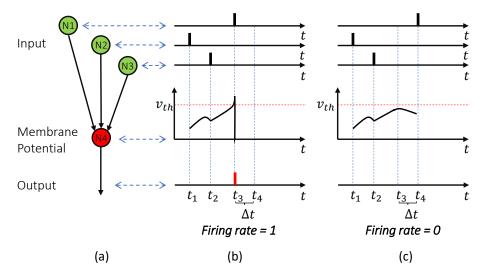

| 1.5 | Neuron firing rate over different input arrival times: (a) Example of a post-synaptic neuron (N4) receiving incoming spikes from three presynaptic neurons, (b) Firing rate =1, (C) Firing rate =0                                                                                                                                                                          | 8  |

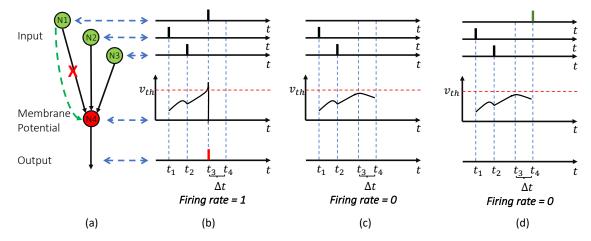

| 1.6 | Example of the connection-fault effect on the firing rate: (a) a postsynaptic neuron (N4) receiving incoming spikes from three presynaptic neurons, (b) with no connection fault, the firing rate = 1, (c) with the N1-to-N4 connection fault, the firing rate = 0, (d) long latency of a connection with an inefficient routing algorithm resulting in the firing rate = 0 | 9  |

| 1.7 | Dissertation organization                                                                                                                                                                                                                                                                                                                                                   | 12 |

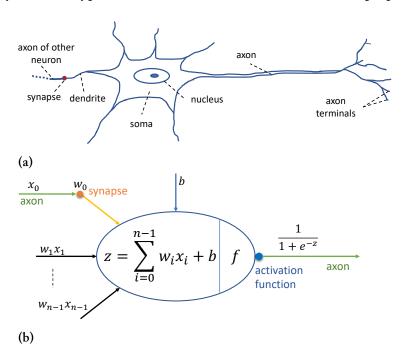

| 2.1 | (a) a cartoon drawing of a biological neuron (b) a mathematical model of a neuron                                                                                                                                                                                                                                                                                           | 16 |

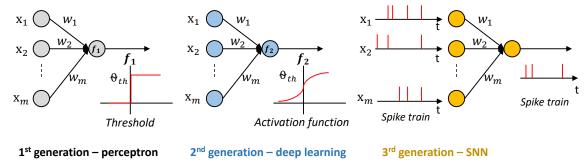

| 2.2 | Generations of artificial neural network                                                                                                                                                                                                                                                                                                                                    | 17 |

| 2.3 | Some common neural network topologies                                                                                                                                                                                                                                                                                                                                       | 18 |

| 2.4 | Synapse implementation: (a) Analog: memristor bridge synaptic circuit [48]. Digital: (b) 12T scheduler SRAM Cell (simplified) (c) 6T core SRAM cell [16]                                                                                                                                                                                                                    | 21 |

| 2.5 | A comparison of spiking neuron models in terms of implementation cost and biological plausibility [77].                                                                                                                                                                                                                                                                     | 26 |

| 2.6 | The Hodgkin-Huxley model: (a) the schematic diagram presents the membrane potential, in which current injection starts at $t = 5$ ms as (b), while (c) and (d) show the dependency of the gating variables $n$ , $m$ and $b$ on the membrane potential $v$ [79].                                                                                                                                                | 27 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

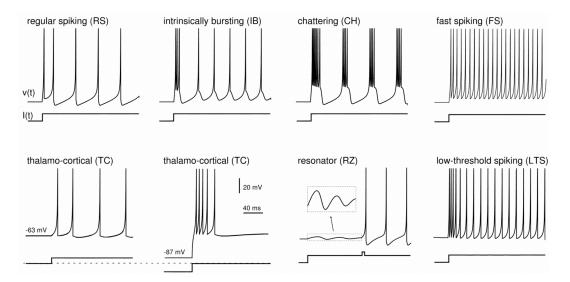

| 2.7 | Known types of the Izhikevich neuron with different values of the parameters a, b, c, d [80].                                                                                                                                                                                                                                                                                                                   | 28 |

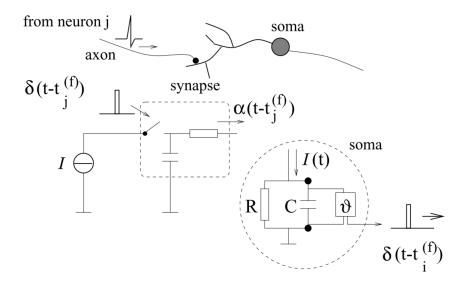

| 2.8 | Schematic diagram of the LIF model (soma, the circuit is in the dashed circle) [13]                                                                                                                                                                                                                                                                                                                             | 29 |

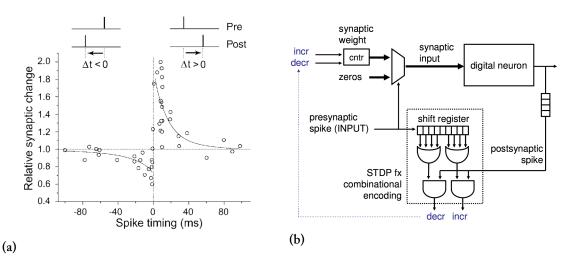

| 2.9 | STDP: (a) Spike-timing window of STDP characterized in hippocampal cultures [86] (b) a minimum complexity digital implementation of STDP [87]                                                                                                                                                                                                                                                                   | 30 |

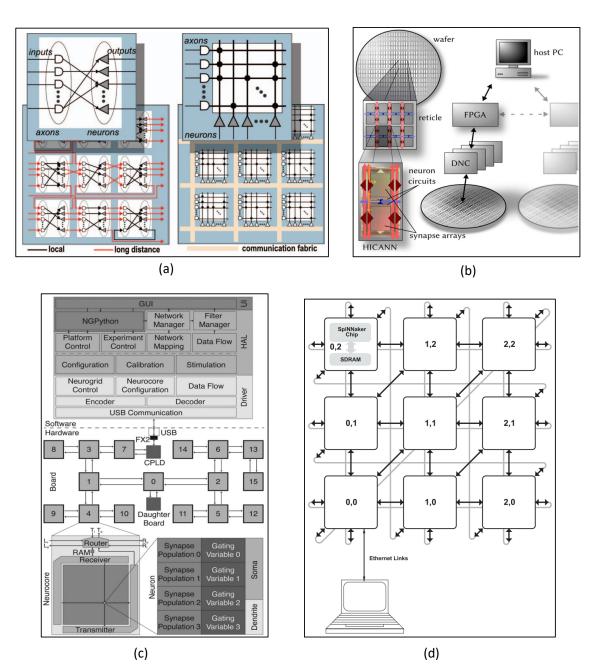

| 3.1 | (a) TrueNorth: consisting of neurosynaptic cores, tiled in a 2D array: logical representation (left) and physical implementation (right) [117]. (b) The architecture of the BrainScaleS wafer-scale hardware system [118]. (c) Neurogrid architecture: software and hardware [116] (d): SpiNNaker consists of computational units using ARM processors and a 2D triangular mesh interconnect architecture [119] | 36 |

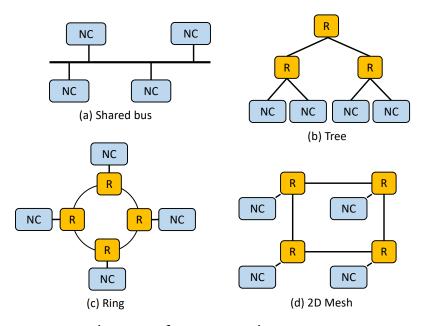

| 3.2 | Interconnect architectures for neuromorphic systems                                                                                                                                                                                                                                                                                                                                                             | 38 |

| 3.3 | Summary of SNN routing methods on various interconnect platforms.                                                                                                                                                                                                                                                                                                                                               | 39 |

| 3.4 | Multicast routing mechanisms: (a) Unicast-based (b) Path-based (c) Tree-                                                                                                                                                                                                                                                                                                                                        | 37 |

| J   | based                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

| 3.5 | Taxonomy of fault-tolerant approaches for neural network architectures                                                                                                                                                                                                                                                                                                                                          | 44 |

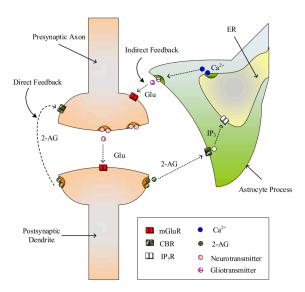

| 3.6 | A self-detect and self-repair mechanism mimicking capability in the human brain [144]. This mechanism is based on indirect feedback from the astrocyte cell (i.e., the most abundant type of glial cell in the brain), by regulating the synaptic transmission probability of release when faults occur.                                                                                                        | 46 |

| 4.1 | 3D mesh NoC architecture with <i>n</i> neural tiles (PEs)                                                                                                                                                                                                                                                                                                                                                       | 51 |

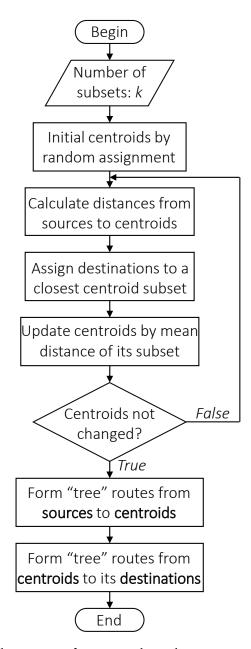

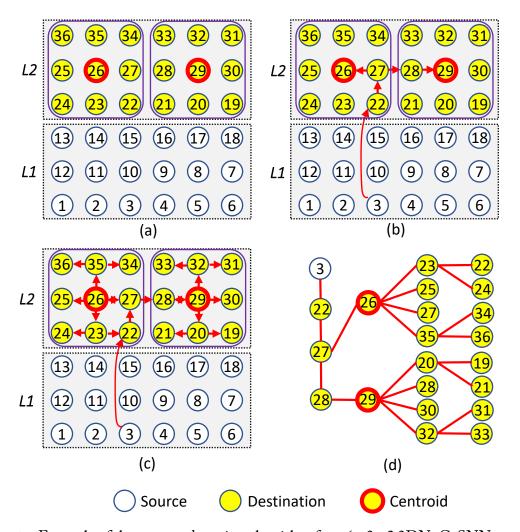

| 5.1 | Flowchart of the proposed routing algorithm.                                                                                                                                                                                                                                                                                                                                                                    | 67 |

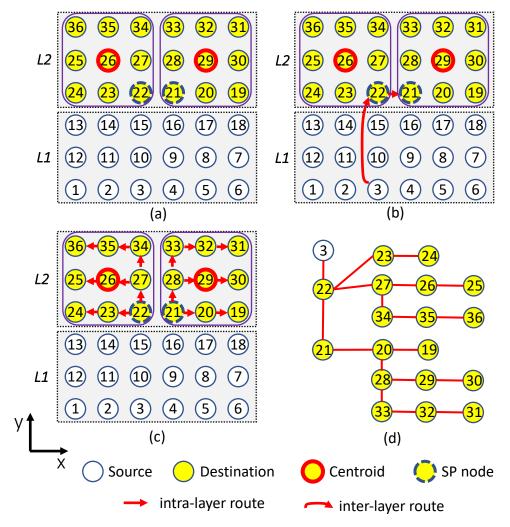

| 5.2 | Example of the proposed routing algorithm for a $6\times3\times2$ 3DNoC-SNN system, where nodes in $L1$ send spike packets to all nodes in $L2$ : (a) destinations are partitioned by adopting K-means clustering with centroids $26$ and $29$ , (b) the formation of the first path of the tree from a given source (node $3$ ) to centroids, (c) the second part of the tree from centroids to its            |    |

|     | destinations, (d) the routing tree from the given source to destinations                                                                                                                                                                                                                                                                                                                                        | 70 |

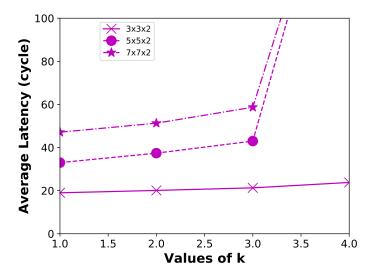

| 5.3 | Average latency under varying the values of k                                                                                                                                                                                                                                                                                                                                                                   | 72 |

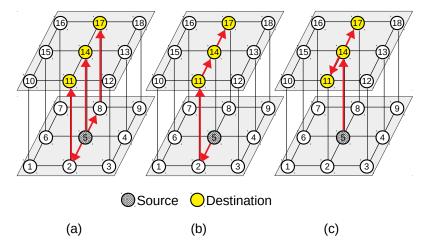

| 5.4  | Example of SP-KMCR for a $6\times3\times2$ 3DNoC-SNN system, where nodes               |

|------|----------------------------------------------------------------------------------------|

|      | in $L1$ send spike packets to all nodes in $L2$ : (a) destinations are partitioned     |

|      | by adopting K-means clustering with centroids 26 and 29, (b) the forma-                |

|      | tion of the first path of the tree from a given source (node 3) to shortest            |

|      | path node of each subgroup (SP node), (c) the second part of the tree from             |

|      | SP nodes to its destinations, (d) the routing tree from the given source to            |

|      | destinations                                                                           |

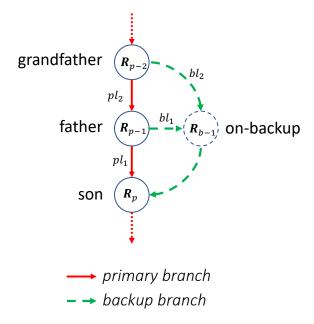

| 5.5  | Primary and backup branches                                                            |

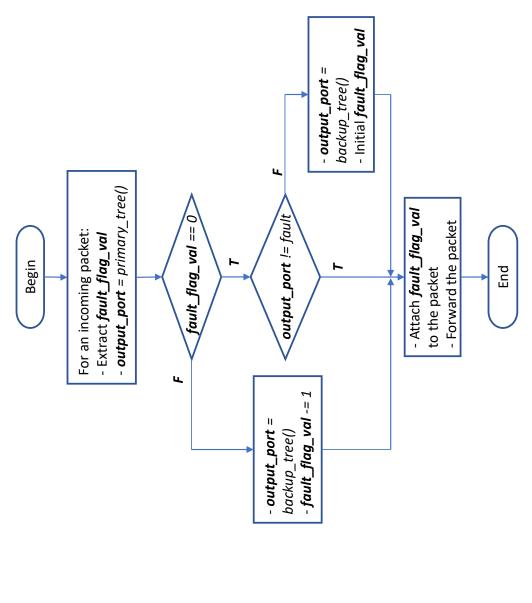

| 5.6  | Fault-management algorithm applied for "son", on-backup, "father" and                  |

|      | "grandfather" routers                                                                  |

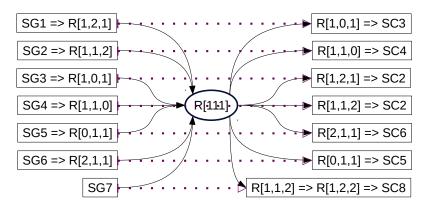

| 6.1  | Block diagram of system architecture                                                   |

| 6.2  | Spiking Neuron Processing Core (SNPC) architecture                                     |

| 6.3  | Spike packet format                                                                    |

| 6.4  | Multicast Spike 3D Router architecture (MC-3DR)                                        |

| 6.5  | Block diagram of routing table architecture. D, U, W, S, E, N, L stand for             |

|      | Down, Up, West, South, East, North, Local respectively 91                              |

| 6.6  | Block diagram of Random Access Buffer (RAB) [164]                                      |

| 6.7  | Block diagram of Bypass-Link-on-Demand [164]                                           |

| 6.8  | Fault-tolerant TSV architecture: (a) router wrapper (b) sharing TSV ar-                |

|      | chitecture with TSV cluster (red rectangles) and sharing arbitrators (S-UP,            |

|      | S-DOWN) [165]95                                                                        |

| 6.9  | Layer-to-layer mapping method                                                          |

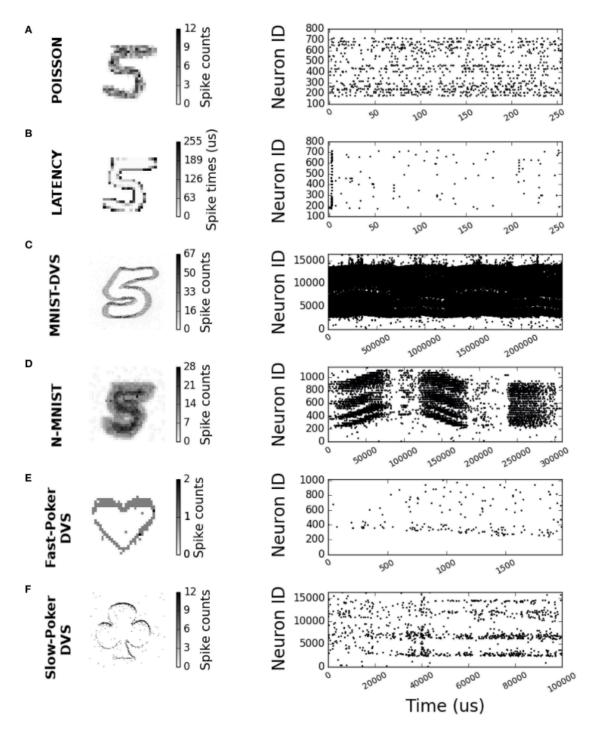

| 6.10 | 2-D histograms and raster plots for different encoding schemes and neu-                |

|      | romorphic data sets. (A) Poisson 28 × 28 input size sample. (B) Latency                |

|      | $28 \times 28$ input size sample. (C) MNIST-DVS $128 \times 128$ input size sample.    |

|      | (D) N-MNIST $34 \times 34$ input size sample. (E) Fast-Poker DVS $32 \times 32$        |

|      | input size sample. (F) Slow-Poker DVS 128 × 128 input size sample [171]. 97            |

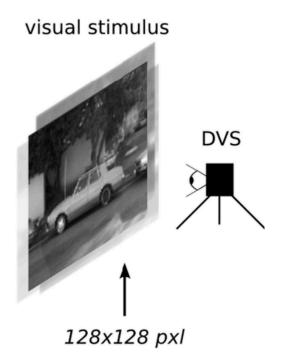

| 6.11 | Conversion using a DVS camera, captured from [172]. In this setup, two                 |

|      | different classes of images (here motorbikes or cars) are displayed on a               |

|      | screen with a small jitter applied at 10Hz. A random subset of the spikes              |

|      | is emitted by the DVS                                                                  |

| 7.1  | Setup for SIR evaluation                                                               |

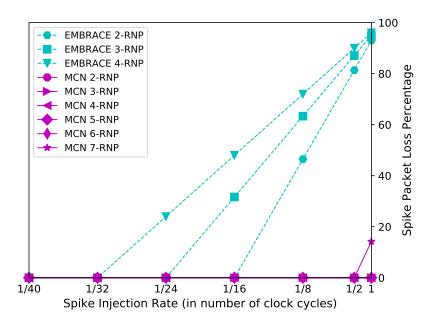

| 7.2  | Router acceptance rate (RAR) comparison when varying the number of router RNP and SIRs |

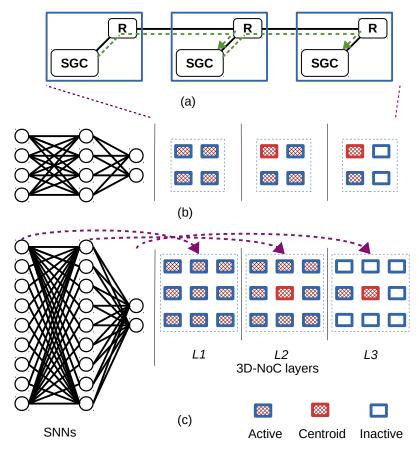

| 7.3  | Layer-to-layer application mapping: (a) block diagram of a node in each                |

|      | layer (b) Inverted pendulum (c) Wisconsin data-set                                     |

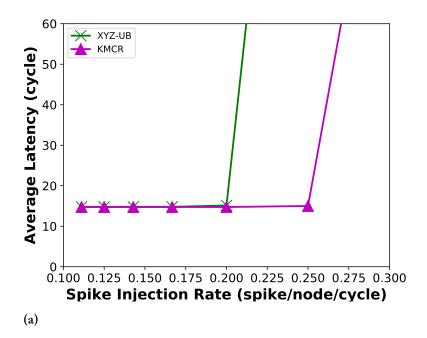

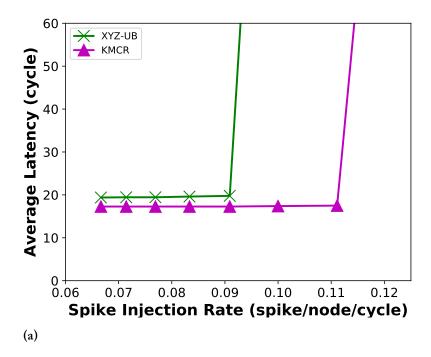

| 7.4  | Average latency over various SIRs for Inverted Pendulum in: (a) 3D Do-                 |

|      | main (b) 2D Domain                                                                     |

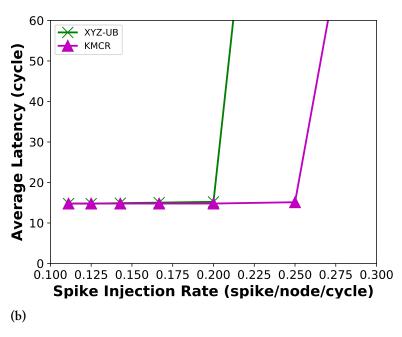

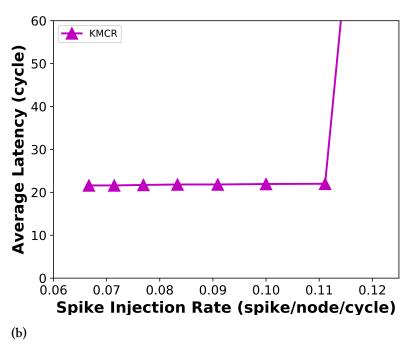

| 7.5  | Average latency over various SIRs for Wisconsin Data-set in: (a) 3D do-  |     |

|------|--------------------------------------------------------------------------|-----|

|      | main (b) 2D Domain                                                       | 106 |

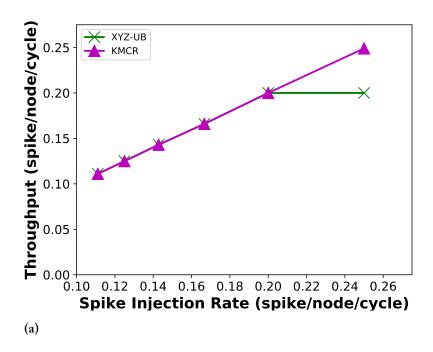

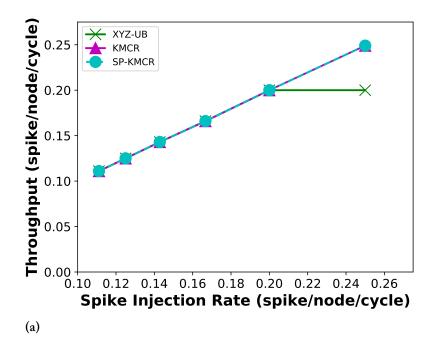

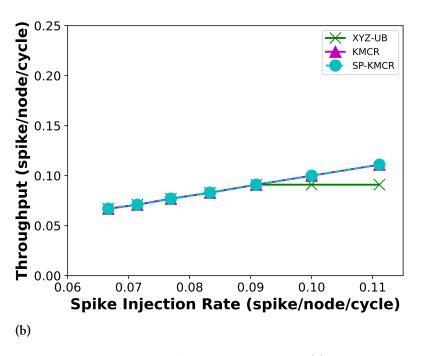

| 7.6  | Average throughput in NoC systems over various SIRs for Inverted Pen-    |     |

|      | dulum in: 3D Domain, (b) 2D Domain                                       | 108 |

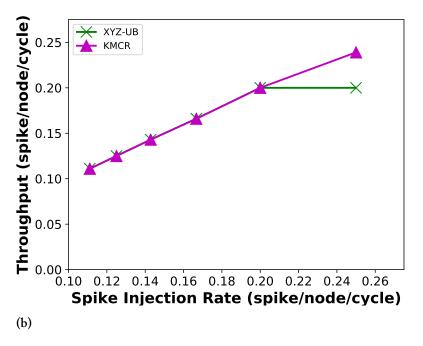

| 7.7  | Average throughput in NoC systems over various SIRs for Wisconsin        |     |

|      | Data-set in: (a) 3D Domain, (b) 2D Domain                                | 109 |

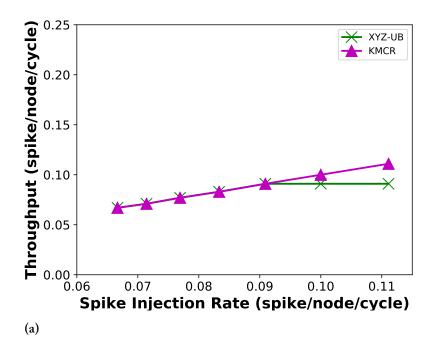

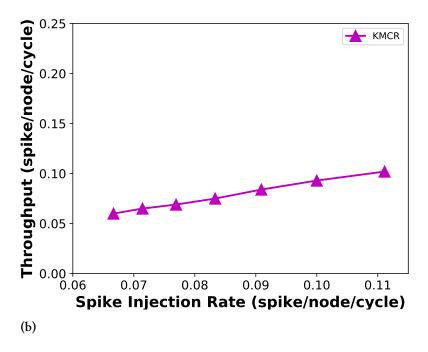

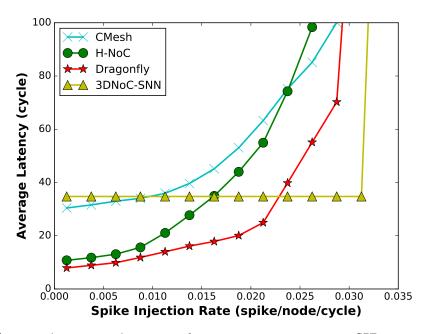

| 7.8  | Average latency evaluation and comparison over various SIRs              | 110 |

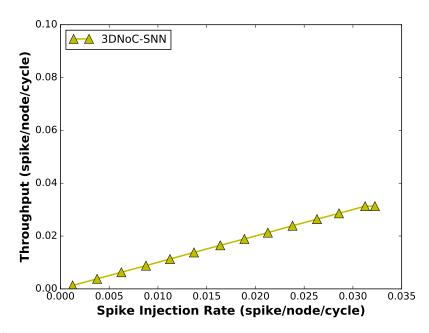

| 7.9  | Average throughput under the synthetic benchmark over various SIRs       | 111 |

| 7.10 | Average latency over various SIRs in 3D domain: (a) Inverted Pendulum    |     |

|      | (b) Wisconsin Data-set                                                   | 113 |

| 7.11 | Average latency over various SIRs in 2D domain: (a) Inverted Pendulum    |     |

|      | (b) Wisconsin Data-set                                                   | 114 |

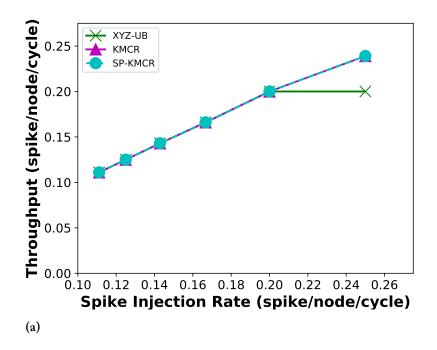

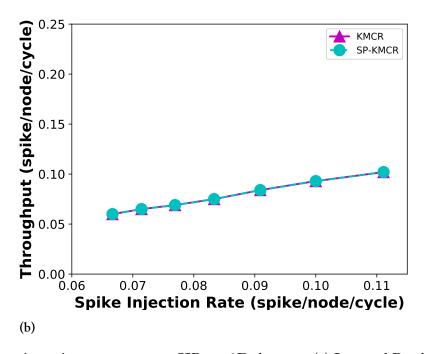

| 7.12 | Average throughput over various SIRs in 3D domain: (a) Inverted Pen-     |     |

|      | dulum (b) Wisconsin Data-set                                             | 116 |

| 7.13 | Average throughput over various SIRs in 2D domain: (a) Inverted Pen-     |     |

|      | dulum (b) Wisconsin Data-set                                             | 117 |

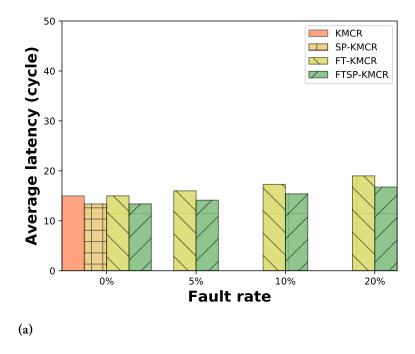

| 7.14 | Average latency over various fault rates: (a) Inverted Pendulum (b) Wis- |     |

|      | consin Data-set.                                                         | 118 |

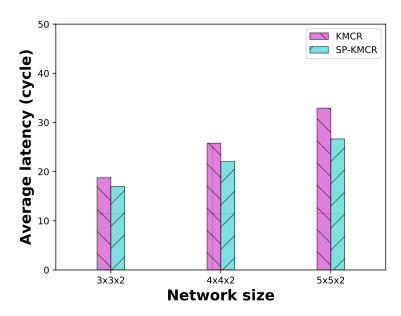

| 7.15 | Average latency comparison of KMCR and SP-KMCR over different network    |     |

|      | sizes                                                                    | 119 |

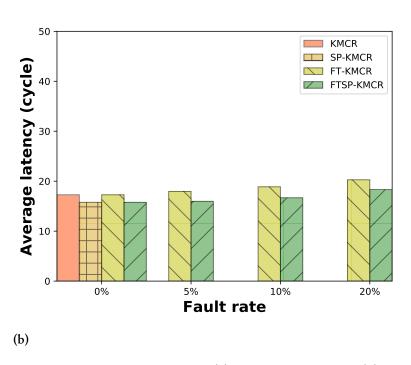

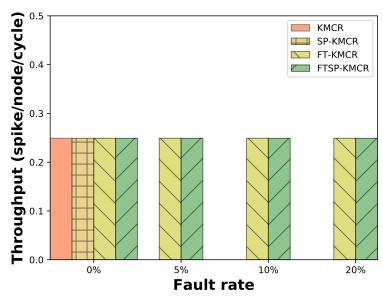

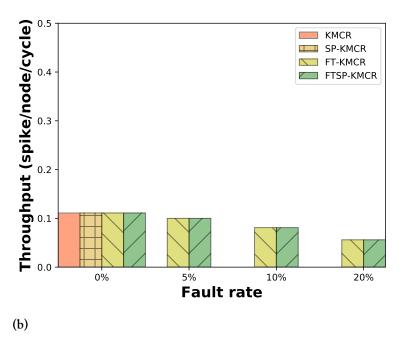

| 7.16 | Average throughput over various fault rates: (a) Inverted Pendulum (b)   |     |

|      | Wisconsin Data-set.                                                      | 121 |

# LIST OF TABLES

| 1.1        | Comparison of von Neumann and Neuro-inspired computing 4             |

|------------|----------------------------------------------------------------------|

| 2.1        | Platform comparison for neuromorphic implementation [62] 22          |

| 4.1<br>4.2 | 2D mesh NoC [23] vs 3D mesh NoC analyzed for Hopfield NN             |

| 7.1        | Realistic simulation configuration                                   |

| 7.2        | Synthetic simulation setup                                           |

| 7.3        | MC-3DR Hardware Complexity Evaluation and Comparison 111             |

| 7.4        | Power consumption of UCB-XYZ and KMCR under realistic benchmarks.112 |

| 7.5        | Power consumption of the KMCR and FTSP-KMCR under the bench-         |

|            | marks                                                                |

## List of Abbreviations

2D-NoC Two dimensional Network-on-Chip

3D-IC Three dimensional Integrated Circuit

3D-NoC Three dimensional Network-on-Chip

3D-SIC Three dimensional Stacked Integrated Circuit

ASIC Application-Specific Integrated Circuit

ANN ARTIFICIAL NEURAL NETWORK

BLoD Bypass-Link-on-Demand

BC Broadcast

CPU CENTRAL PROCESSING UNIT

CT CROSSBAR TRAVERSAL STAGE

DRAM Dynamic Random Access Memory

ECC Error Correction Codes

FIFO FIRST-IN-FIRST-OUT

FT-KMCR FAULT-TOLERANT K-MEANS BASED MULTICAST ROUTING

${\bf ALGORITHM}$

FTSP-KMCR FAULT-TOLERANT SHORTEST-PATH KMCR

HDL HARDWARE DESCRIPTION LANGUAGE

HF HOPFIELD NEURAL NETWORK

IC INTEGRATED CIRCUIT

KMCR K-means based MultiCast Routing algorithm

MC Multicast

NoC NETWORK-ON-CHIP

PE PROCESSING ELEMENT

RAB RANDOM-ACCESS-BUFFER

RC ROUTING COMPUTATION STAGE

RNDC RANDOMLY CONNECTED NEURAL NETWORK

RTL REGISTER-TRANSFER LEVEL

SA Switch Allocation stage

SRAM STATIC RANDOM ACCESS MEMORY

SNN Spiking Neural Network

SNPC Spiking Neural Processing Core

SoC System-on-Chip

SP-KMCR SHORTEST- PATH K-MEANS BASED MULTICAST ROUTING

ALGORITHM

TSV THROUGH SILICON VIA

UC UNICAST

# Acknowledgments

First, I would like to convey my deepest gratitude to my supervisor Prof. Abderazek Ben Abdallah for his guidance, support, and encouragement. Also, I would like to thank Prof. Toshiaki Miyazaki, Prof. Tsuneo Tsukahara, Prof. Junji Kitamichi of The University of Aizu and Prof. Hideharu Amano of Keio University for taking the time to revise my thesis. Moreover, my sincere gratitude to Prof. Yuichi Okuyama for his help and support during the past three years.

Aizu is really memorable for me because of my great friends and colleagues. I am thankful to Dr. Akram Ben Ahmed of Keio University and Dr. Dang Nam Khanh of Vietnam National University for their significant help and discussion. I want to thank all the members of the Adaptive Systems Laboratory and my friends at The University of Aizu. Their supportive words and encouraging messages kept me motivated to work harder and be a better researcher and person. Not to forget to appreciate the staff of The University of Aizu for their assistance.

My endless love goes to my parent and family who always endow me with infinite support and unconditional love. Last but not least, my most heartfelt thanks are due to my dearest stunning wife, *Hien-san*. She always stood by me and endowed me with her endless love and support.

Vu Huy The, September 2019, Aizu, Japan

# Algorithms and Architectures for Spiking Neuromorphic Systems

Thesis advisor: Professor Abderazek Ben Abdallah

#### Abstract

Inventing the powerful machine like the human brain has been a driving force in computing for decades. The von Neumann architecture has been considered to be a clear standard for such the system. However, the significant differences in the organization, power consumption requirements, and the computational power of von Neumann architecture compared to a biological brain leads to creating alternative architectures. Brain-inspired computing or neuromorphic computing is a biologically inspired approach created from highly connected neurons to not only model neuroscience theories but also solve machine learning problems. The term neuromorphic was first introduced by Carver Mead in 1990, where it referred to very large scale integration (VLSI) with analog components to mimic biological neural systems.

In recent years, artificial neural networks (ANNs) with efficient learning methods (e.g., backpropagation) have shown a remarkable improvement in terms of accuracy (even better human-level) for large-scale visual/auditory recognition and classification tasks. Particularly, the convolution neural network (CNN) and recurrent neural network (RNN) have shown promising tools for a wide range of applications such as image, video, and speech. To reach considerable achievement, state-of-the-art neural networks, however, tend to deeply increase their number of layers and size (i.e., deep learning). Consequently, they require hardware platforms with a huge amount of computation as well as power consumption. On the other hand, spiking neural networks (SNNs) was proposed to not only mimic efficiently the behavior of biological neurons but also make neuromorphic systems extremely power-efficient with tens of pJ per connection.

However, implementing a scalable interneuron communication architecture is one of the major challenges for hardware-based SNNs. The architecture is required to maintain a huge amount of traffic created from a massive number of neurons and synapses accommodated on neural computation units. Furthermore, since the arrival time of spikes is used to encode the information, timing violation in such communication architecture affects the overall performance of SNNs. A shared bus as a communication medium is a poor choice for implementing a large-scale complex SNN chip/system because adding neurons decreases the communication capacity of the chip and may affect the neuron's firing rate due

to increasing length of the shared bus. Moreover, the nonlinear increase in neural connectivity is too significant to be directly implemented using a dedicated point-to-point communication scheme. Two-dimensional packet-switched network-on-chip (2D-NoC) has been considered as a potential solution to deal with the interconnection problems found in previously proposed shared communication medium based SNNs. However, such interconnect strategies make it difficult to achieve a high level of parallelism and scalability with low power consumption, especially in large-scale SNN chips.

We also consider three-dimensional network on chips (3D-NoCs) which take advantage of 3D Integrated Circuits (3D-ICs) and mesh-based network on chip (NoCs) opening a promising architecture for SNNs. They offer scalability and parallelism of NoCs that are enhanced in the third dimension thanks to the short wire length and the low power consumption of 3D-ICs interconnects. Consequently, 3D-NoCs are considered to be one of the most advanced and suitable for SNN systems, with capabilities of extremely high bandwidth, efficient scalability, and low power. However, to take the advantages for SNNs, 3D-NoC demands an efficient multicast routing algorithm to deal with a high traffic pattern where a presynaptic neuron sends spikes to a subset of postsynaptic ones. Furthermore, due to the complex nature of 3D-ICs and the continuing shrinkage of the semiconductor components, 3D-NoC based systems are becoming susceptible to a variety of faults. Especially in SNNs, when connections are faulty, the post-synaptic neuron becomes silent or near-silent (i.e, firing rate reduction). This may degrade overall system performance.

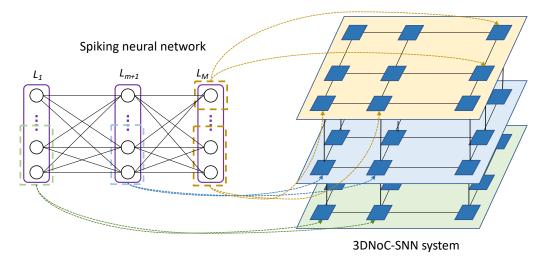

Starting from the facts mentioned above, this dissertation proposes algorithms and architectures for spiking neural network systems based on 3D-NoC (3DNoC-SNN). First, a performance assessment for 3DNoC-SNN is presented to analyze the system performance with different spiking neural network topologies, spike routing methods (i.e., unicast, multicast and broadcast), and in both with and without faults occurring in the system. This analytical model aims to early analyze the system architecture before actual implementation. Second, this dissertation proposes novel multicast spike routing algorithms which are a combination of k-means clustering and tree-based routing method. Adopting k-means is as a partition method helping to get overall balanced traffic and then improve system performance. Moreover, a fault-tolerant multicast routing algorithm is also proposed to deal with connection faults in the system, in which primary and backup routing paths are pre-defined. When faults appear in the primary route, routers switch incoming spike packages via the backup path. This reduces recovery overhead, average latency, and enables the system to avoid timing violation of SNNs. Finally, architecture and hardware design and evaluation of the proposed 3DNoC-SNN system are presented to evaluate the proposed works, as well as compare with the analytical model.

## スパイキングニューロモルフィックシステムのためのアルゴリズム 及びアーキテクチャ

概要

数十年にわたり、人間の脳のような強力な計算機を発明することがコンピュータの分野においての原動力とされてきた。フォン・ノイマン型アーキテクチャは、これらのようなシステムにおいて、明らかな基準とされている。しかし、その構成における重大な違いである、電力消費量、生物の脳に比べたフォン・ノイマン型アーキテクチャの計算能力は、新たなアーキテクチャの創出につながった。脳に想起された、もしくは、脳の構造を模した計算システムという新たな計算手段は、高度に結びついている神経細胞から創出され、人間の脳構造を模した理論を形成するだけでなく、機械学習における問題を解くことにつながっている。"Neuromorphic"という専門用語は1990年にCarver Meadにより最初につくられたものであり、それはアナログな部品を付帯した超大規模集積回路(VLSI)による生物的神経細胞システムの模倣を指したことばからきている

近年では、人工神経細胞ネットワーク(ANNs)と、誤差逆伝搬法のような効率的な学習手法が、大規模な視覚・聴覚的認識と分類において、精度の観点から、顕著な功績を示しており、それはときに人間のレベルを凌駕することもあった。特に、畳み込みニューラルネット(CNN)と再帰型ニューラルネットは、画像、動画、音声のような幅広い分野における有望なツールとしての成果を示している。著しい成果、最先端なニューラルネットに達するとき、そこには深層ニューラルネットとよばれるような、深く増加された層や大きさのネットワークが形成される。結果として、それらは大規模な計算量と消費電力を必要とするハードウェアプラットフォームを必要とする。一方で、スパイキングニューラルネット(SNN)は、生物の神経細胞を効率的に模倣するだけでなく、非常に電力効率の良い脳の構造を模したシステムの構成(一つの結びつきにつき、数十 pJ 程度)を可能にする。

しかしながら、拡張可能な神経細胞の通信アーキテクチャを実装することは、ハードウェアを基盤とした SNN の実装における大きな課題となっている。そのアーキテクチャは、膨大なニューロンとその計算に用いられる接続部における、大規模な通信網の制御性を維持することが必要とされしまう。さらに、スパイクの到達時間はデータの加工に用いられ、タイミング違反は SNN の処理全体に影響を与えてしまう。通信手段としての共有バスは、ニューロン数を増やすことは通信容量を減少させることにつながるため、大規模で複雑な SNN 回路/システムの実装において乏しい選択であり、共有バスの長さを増加させることからそれはニューロンの発火率に影響するとされる。さらに、ニューロンの接続における非線形的増加はとても著しく、ポイント・ツー・ポイント型の通信に適用されるような直接の接続は実装できない。二次元パケットスイッチ型ネットワーク・オン・チップ(NoC)は、先で述べられたような共有バスを媒体とした SNN の実装おける相互通信問題に対する潜在的な解決策として考えられている。しかし

ながら、そのような相互通信における戦略は、高い並列性と拡張性および大規模な SNN 回路における低消費電力を獲得する上で大きな困難を要することにつながる。

私たちは、SNN において有望なアーキテクチャとされる 3次元階層における集積に利点を持つ 3次元ネットワーク・オン・チップについても考えます。それらは、3次元化することにより縮小されたワイヤーのおかげで、ネットワーク・オン・チップにおいての拡張性と並列性を提供する。結果として、非常に高い帯域幅と効率的な拡張性、低消費電力により、3次元型 NoC はもっとも SNNのシステムにおいて最も適しているとされるものの中の一つである。しかしながら、SNNにおいてこのような利点を受けるために、3次元型 NoC は、高度な交通形態に対処するための、効率的なマルチキャストルーティングアルゴリズムを必要とする。さらに、3次元型 NoC の複雑性と継続的なセミコンダクタ部品の縮小により、3次元型 NoC を元ととしたシステムは様々な欠陥に対して影響を受けやすくなってしまう。特に SNNにおいて、接続に欠陥が生じた場合、ポストシナプティックなニューロンは、発火率の現象に見られるような、静もしくはほとんど静な状態になってしまう。これはシステム全体の性能を低下させてしまう。

以上に述べられた事実をはじめ、この論文では3D-NoC をベースとした スパイキングニューラルネット(3D-NoC-SNN)のためのアルゴリズムとアーキテ クチャを提案する。第一に、3DNoC-SNN の性能評価は、ユニキャスト、マル チキャスト、ブロードキャストのようなスパイクルーティングの方法、そしてシ ステムに発生する欠陥のあるかないかにおいて、異なるトポロジーの SNN との 比較で行われた。第二に、この論文は画期的な、k-平均法とツリーベースのルー ティング方法の組み合わせによるマルチキャストスパイクルーティングアルゴリ ズムについて提案する。分割方法としてk-平均法を採用することは、全体的にバ ランスの取れた交通を可能にし、システムの性能を向上させることにつながった。 さらに、フォールトトレラントなマルチキャストルーティングアルゴリズムは、 主要な経路とバックアップ経路を設けることにより、システムにおける接続の欠 落に対処することにも役立てられた。主要ルートにおいて欠陥が現れた時、ルー ターはバックアップ経路を用いて、入力スパイクのパッケージを切り替える。こ れは復旧にかかるオーバーヘッド、平均遅延を削減し、システムがタイミング違 反を回避することを可能とした。最後に、アーキテクチャとハードウェアの設計 と提案された 3D-NoC-SNN システムは、解析的な比較により提案された仕事に ついての評価を示した。

1

# Introduction

# 1.1 Brain-inspired Computing: Towards a New Computation Paradigm

### Von Neumann Architecture

The Von Neumann architecture, that was presented 60 years ago, is still a solid base for computer design. The architecture operates in a sequential manner where data is fetched from memory. This concept is very powerful in building supercomputing machines used in a wide range of applications such as quantum mechanics, weather forecasting, climate research, and so on. However, the architecture has faced challenges: (1) in the traditional von Neumann architecture, both data and instructions are stored in the memory, as shown

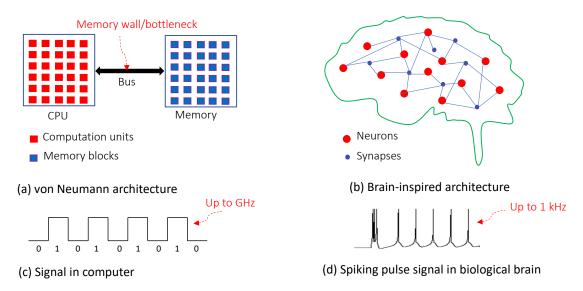

Figure 1.1: Computation paradigm is shifted from (a) von Neumann (centric computation) to (b) brain-inspired computing (distributed computation).

in Figure 1.1 (a). From this, the CPU can fetch the instructions from the memory and compute arithmetic operations on the data; it however cannot do both at the same time. Consequently, this results in the well-known memory wall problem of the data movement between the CPU and the memory which has become the bottleneck of the entire system [1]. (2) The continued success of the development of the modern von Neumann computing system was secondly enabled by increasing the transistor integration density, followed by the multicore architecture. This was presented in Moore's law predicting that the integration density is doubled every 18 months. The silicon semiconductor industry has shown extraordinary achievements throughout its history. However, since the density of data continuously escalates, extracting valuable information from this huge amount of data becomes computationally expensive, even for supercomputers. Furthermore, when transistors are getting smaller and their power density keeps constant, the questions of domination of dynamic power and the increase in leakage current [2] are raised. Consequently, this slows down the transistor switching rate as well as the overall speed of the system if an efficient cooling mechanism is not employed.

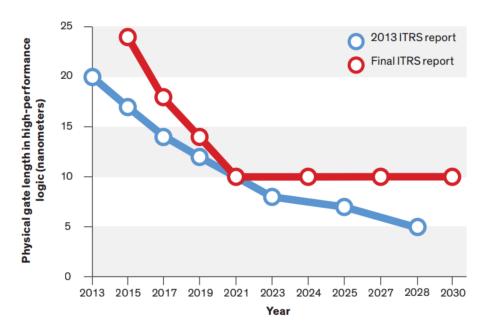

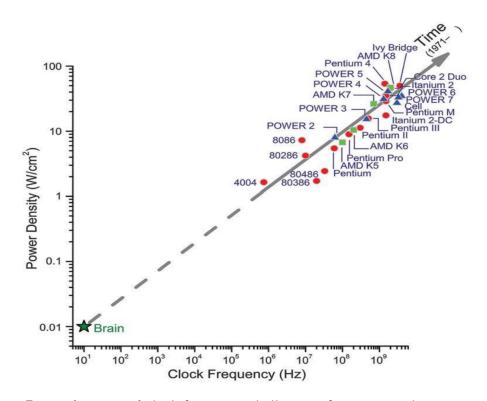

As the end of Moore's law seems closer than ever (see Figure 1.2), computer scientists

Figure 1.2: End of the road - a shringking challenge of of physical gate length at 10nm [3].

Figure 1.3: Power density and clock frequency challenges of conventional computing architecture [4].

Table 1.1: Comparison of von Neumann and Neuro-inspired computing.

| von Neumann                   | Neuro-inspired computing      |

|-------------------------------|-------------------------------|

| Very high operation frequency | Low operation frequency (KHz) |

| (GHz)                         |                               |

| Centric computation           | Distributed computation       |

| Low parallelism               | High parallelism              |

| Low power efficiency          | High power efficiency         |

have been exploring to build machines as complex and efficient as our brain, dealing with power density and clock frequency challenges of the conventional architecture, as shown in Figure 1.3. Our brain works completely different compared to traditional von Neumann architecture. In fact, there are many secrets behind how the human brain works. What we know is that it distributes computation and memory (see Figure 1.1(b)) among 100 billion biological neurons, and each of them is highly connected with thousands of others via synapses. Neurons communicate with each other through spikes (i. e., short electrical pulses or spikes). The brain is a powerful computation system that helps us survive, adapt, and predict while consuming tens of watts, as summarized in Table 1.1.

### Brain-inspired Computing

Brain-inspired computing or neuromorphic computing is a biologically inspired approach created from highly connected neurons to not only model neuroscience theories but also solve machine learning problems. The term neuromorphic was first introduced by Carver Mead in 1990 [5], where it referred to very large scale integration (VLSI) with analog components to mimic biological neural systems. Such systems can be categorized as non-spiking and spiking approaches. First, the non-spiking approach is referred to as the implementation of traditional artificial neural networks (ANNs), in which it aims to improve throughput over power (or acceleration purpose). In recent years, ANNs have shown a remarkable improvement in terms of accuracy (even better human-level [6]) for large-scale visual/auditory recognition and classification tasks. Particularly, the convolution neural network (CNN) [7] and recurrent neural network (RNN) [8] have shown promising tools for a wide range of applications such as image, video, and speech. Nowa-

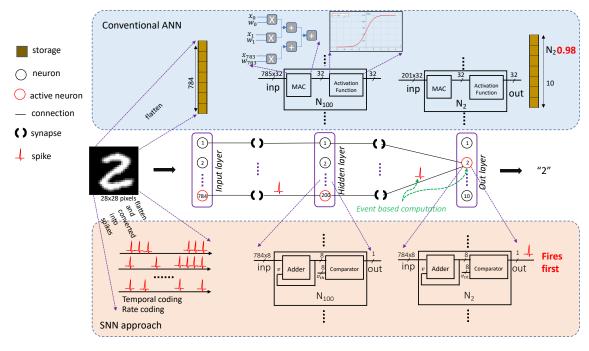

Figure 1.4: An illustration of ANN and SNN hardware implementations for a handwritten digit recognition application.

days, they are typically trained by using graphic processing units (GPUs) or on the cloud side. To reach considerable achievement, state-of-the-art neural networks tend to deeply increase their number of layers and size (i.e., deep learning). For example, Residual Network (ResNet) [9] has 152 layers to achieve 3.57% error on the ImageNet test set (1st place on the ILSVRC 2015 classification challenge [10]). However, this leads to challenges for hardware systems in terms of computation, memory and communication resources. For example, Google's autoencoder [11] was implemented on a cluster of 16,000 processing cores consuming ~100 kW of power to successfully recognize faces of cats from ten million images captured from YouTube videos.

The second approach based on spiking neural networks (SNNs), witnesses increasing attention both to gain a better understanding of the brain and to explore novel biologically-inspired computations. SNNs have been successfully applied for solving practical problems such as visual recognition and classification tasks [12]. Besides, implementations of neuromorphic hardware have enabled large-scale networks to run in real-time, which

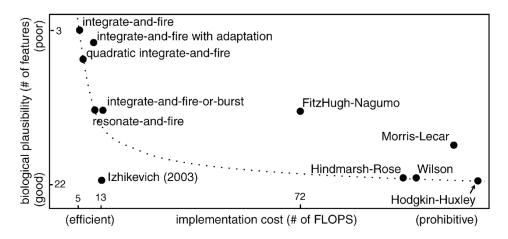

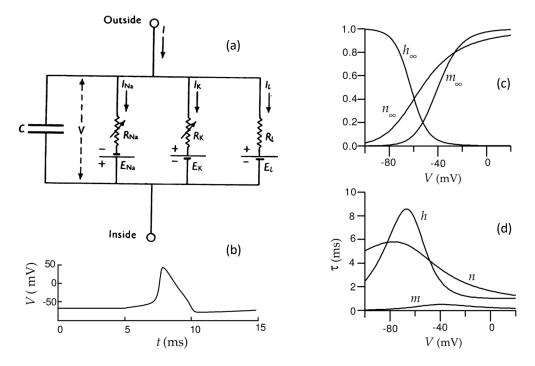

is a critical requirement for several applications, including neuro-robotics control, brainmachine interfaces, and robotic decision making. In principle, SNNs attempt to mimic the information processing in the mammalian brain based on parallel arrays of neurons which communicate via spike events. Unlike the typical multi-layer perceptron networks where neurons fire at each propagation cycle, the spiking neurons fire only when a membrane potential reaches a specific value. In SNN, information is encoded using various encoding schemes, such as coincidence coding, rate coding or temporal coding [13]. There have been many spiking neuron models proposed. SNN typically employs integrate-andfire neurons model [14] in which a neuron generates voltage spikes (roughly 1ms in duration per spike) that can travel down nerve fibers if it receives enough stimuli from other neurons with the presence of external stimuli. These pulses may vary in amplitude, shape, and duration, but they are generally treated as identical events. To better model, the dynamics of the ion channel in a biological neuron, which is nonlinear and stochastic, the Hodgkin-Huxley [15] conductance-based neuron is often used. However, the Hodgkin-Huxley model is too complicated to be used for a large scale simulation or hardware implementation.

Software simulation of SNN is a flexible method for investigating the behavior of neuronal systems. However, simulation of a large (deep) SNN system in software is slow. An alternative approach is a hardware implementation, which provides the possibility to generate independent spikes accurately and simultaneously output spikes in real-time. Hardware implementations also have the advantage of computational speedup over software simulations and can take full advantage of their inherent parallelism. Hardware implementation of ANN and SNN is explained in Figure 1.4. Specialized hardware architectures with multiple neuro-cores could exploit the parallelism inherent within neural networks to provide high processing speeds with high power-efficiency, which make SNNs suitable for embedded neuromorphic devices and control applications. For example, a TrueNorth chip [16] consists of 4,096 neuro-synaptic cores with one million integrate-and-fire neurons and 256 million SRAM synapses. It consumes only 65 mW of power to

perform real-time (30 frames/s) object recognition tasks.

## 1.2 Motivation: Power, Scaling, and Reliability Challenges

Inventing the powerful machine like the human brain has been a driving force in computing for decades. The von Neumann architecture has been considered to be a clear standard for such a system. However, the significant differences in the organization, power consumption requirements, and the computational power of von Neumann architecture compared to a biological brain leads to creating alternative architectures. As inspired by the biological brain, neuromorphic systems require high computation power that can perform operations in parallel. Such systems are more suitable for real-time applications such as: real-time control [17], real-time digital image reconstruction [18], and autonomous robot control [19]. These systems emphasize many simple processing components (i.e., as a form of neurons) combined with dense interconnections between them (i.e., as the form of synapses). This makes that traditional von Neumann architectures are not able to meet this requirement because of the bottleneck [1] coming from the separation of memory and processing unit. Therefore, there is a high demand for neuromorphic systems that can deal with this bottleneck as well as challenges related to end of Moore's law and the end of Dennard scaling. Furthermore, extremely low power operation is an important motivation at the moment and this is inspired by the human brain which performs extremely complex computations with small power, about 20 watts. It, therefore, motivates us to adopt spiking neural networks (SNNs) in our work instead of artificial neural networks (ANNs).

A major challenge of neuromorphic implementation is scalability. It requires a scalable interneuron communication architecture that can maintain a huge amount of traffic created from a massive number of neurons and synapses accommodated on neuron computation units. Since arrival time of spikes is used to encode the information, timing violation in such communication architecture affects the overall performance of SNNs. A shared bus as a communication medium is a poor choice for implementing a large-scale

Figure 1.5: Neuron firing rate over different input arrival times: (a) Example of a postsynaptic neuron (N4) receiving incoming spikes from three presynaptic neurons, (b) Firing rate =1, (C) Firing rate =0.

complex SNN chip/system with multicast routing because adding neurons decreases the communication capacity of the chip and may affect the neuron's firing rate due to increasing length of the shared bus. Moreover, the nonlinear increase in neural connectivity is too significant to be directly implemented using a dedicated point-to-point communication scheme. Two-dimensional packet-switched network-on-chip (2D-NoC) [20] has been considered as a potential solution to deal with the interconnection problems found in previously proposed shared communication medium based SNNs [21, 22]. However, such interconnect strategies make it difficult to achieve high scalability with low power consumption, especially in large-scale SNN chips. From another hand, the routing algorithm also plays a vital role in neuron communications because it influences the load balance across the network and the overall latency of system [20]. Since the traffic pattern in a given SNN is in a one-to-many fashion, where a presynaptic neuron sends spikes to a subset of postsynaptic ones, the use of conventional unicast-based routing in large-scale SNNs is inefficient [23].

One of the other main problems of hardware implementations for SNNs is their reliability potential. Although it has been claimed that SNNs have some intrinsic fault-tolerance

Figure 1.6: Example of the connection-fault effect on the firing rate: (a) a postsynaptic neuron (N4) receiving incoming spikes from three presynaptic neurons, (b) with no connection fault, the firing rate = 1, (c) with the N1-to-N4 connection fault, the firing rate = 0, (d) long latency of a connection with an inefficient routing algorithm resulting in the firing rate = 0.

properties thanks to their massive and parallel structures inspired by the biological neural models, it is not always the case when it comes to practical cases [24]. In fact, with the challenges inherited from the continuing shrinkage of semiconductor components, the implementation of SNNs in hardware exposes them to a variety of faults [24]. The fault risk becomes even more important as we move towards integrating large-scale SNNs for embedded systems when the yield becomes a major problem [25]. When considering the inter-neuron communication reliability, faults may affect the system performance, especially when they occur in critical applications (e.g., aerospace, autonomous car, biomedical, etc.). Such failures can result in undesirable inaccuracies or even irreversible severe consequences. In SNNs, when faults occur in the inter-neuron connections, the postsynaptic neurons become silent or near-silent (low firing activity). As shown in Figure 1.6 (c), at the presence of a broken link in the N1-to-N4 connection, the membrane potential of N4 fails to reach the threshold that would allow it to fire an output spike, as it is the case in Figure 1.6 (b). This leads to a reduction in the firing rate of the postsynaptic neuron. Consequently, it may have an impact on the overall performance of SNN models based on the rate coding method [26]. Neurons with low firing rates become more susceptible to noisy

firing rates and temporal jitter of spikes resulting in an increase of the variance [27]. As a result, it demands efficient fault-tolerant techniques. In such mechanisms, the recovery time is one of the important requirements. The long latency of a fault-tolerant routing method may influence the firing rate, as shown in Fig. 1.6 (d). It may impact especially, SNN models using a temporal coding method that is based on the relative timing between spikes. Therefore, the challenge to find efficient fault-tolerant solutions is becoming more important with the integration of large SNNs onto silicon. Routing algorithms are considered as one of the most efficient recovery mechanisms in SNNs as they play a vital role in neuron communication performance. In addition, when considering fault-tolerance requirements, the routing algorithm should be carefully chosen in order to minimize the inter-neuron communication latency; otherwise, the postsynaptic node accuracy can be compromised despite the fact that the failure has been worked around. Figure 1.6 (d) illustrates a clear example of such a case. In this figure, we can see that the long latency due to an inappropriate routing can prevent the postsynaptic neuron to timely fire the output spike.

### 1.3 Dissertation Goals and Contributions

In this thesis, we present algorithms and architectures for spiking neural network systems based on 3D-NoC, named 3DNoC-SNN. The system exploits the inherent 3D structure of the brain to reduce the communication distances between neurons and allows the seamless implementation of large-scale SNN-based computing systems. The evaluation results show essential characteristics, such as low-latency, high throughput, maintaining the traffic at high fault-rates and low power footprint that make the proposed architecture suitable for large-scale SNN-based embedded AI implementations. The main contributions of this dissertation are summarized as follows:

1. A performance assessment for 3DNoC-SNN. The assessment is done by providing an analytic model to analyze the system performance with different spiking neural network topologies, spike routing methods (i.e., unicast, multicast and broadcast),

and in both with and without faults occurring in the system. The goal is to provide an efficient and accurate performance assessment to early understand and evaluate the advantages and drawbacks of potential neural network topologies before the actual hardware development of the SNN system.

- 2. Multicast spike routing algorithms for 3DNoC-SNN. In SNNs, a neuron needs to send their output spikes to thousands of others. In addition, neurons also have different spiking operation modes with different spike rates. As a result, an efficient multicast routing method is highly demanded. This thesis proposes novel routing algorithms which are a combination of k-means clustering and tree-based routing method. Adopting k-means is as a partition method helping to get overall balanced traffic and then improve system performance as well.

- 3. A fault-tolerant routing mechanism to deal with link faults in the 3DNoC-SNN system. In SNNs, when faults occur in inter-neuron connection, the postsynaptic neuron becomes silent because it does not receive enough inputs (spikes) from presynaptic ones. To deal with this issue, this thesis proposes a new fault-tolerant routing algorithm where it pre-defines primary and backup routing paths. When faults appear in the primary route, routers switch incoming spike packages via the backup path. This reduces recovery overhead, average latency, and enables the system to avoid timing violation of SNNs.

## 1.4 Dissertation Organization

The remaining parts of this thesis is organized as follows:

- In chapter 2, we first overview neural networks, its generations, and topologies. We then present the fundamental of neural networks and their hardware implementation.

- Chapter 3 presents some of the important related works which deal with inter-

| _ |               |           |                                                                                                                                                                                                                                  |  |  |

|---|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | Back ground   | Chapter 1 | INTRODUCTION Brain-Inspired Computing Motivation Dissertation Goals and Contributions Dissertation Organization                                                                                                                  |  |  |

|   | Back g        | Chapter 2 | NEURAL NETWORK ARCHITECTURES Neural Network and Topology ANN Architectures SNN Architectures                                                                                                                                     |  |  |

|   |               | Chapter 3 | RELATED WORKS Spiking Neuromorphic Systems Inter-neuron Communication Fault-tolerant Neural Network                                                                                                                              |  |  |

|   | Algorithms    | Chapter 4 | COMPREHENSIVE ANALYTICAL PERFORMANCE ASSESSMENT<br>Assumption and Network Model<br>Non-faulty System Assessment<br>Faulty System Assessment                                                                                      |  |  |

|   |               | Chapter 5 | K-MEANS BASED MULTICAST SPIKE ROUTING ALGORITHMS K-means Based Multicast Spike Routing Algorithms Shortest Path K-means Based Multicast Routing Algorithm Fault-tolerant Shortest Path K-means Based Multicast Routing Algorithm |  |  |

|   | Architectures | Chapter 6 | TOWARDS SCALABLE SPIKING NEUROMORPHIC ARCHITECTURE System Architecture Spiking Neuron Processing Core 3D Multicast Router Application Deployment                                                                                 |  |  |

|   |               | Chapter 7 | DESIGN AND EVALUATION<br>Methodology<br>Results                                                                                                                                                                                  |  |  |

|   |               | Chapter 8 | CONCLUSIONS AND FUTURE WORK<br>Conclusions<br>Future Work                                                                                                                                                                        |  |  |

Figure 1.7: Dissertation organization.

neuron connection challenges in neuromorphic systems. Furthermore, we also provide a survey of fault-tolerance in neural network systems.

- Chapter 4 provides an analytical model to assess the performance of 3DNoC-SNN

under different spiking neural network topologies and routing methods. It is conducted under considerations of the fault and no-fault appearance.

- Chapter 5 is dedicated to introducing the proposed multicast routing algorithms.

First, it describes a K-means based multicast routing algorithm (KMCR). It then presents an improved algorithm of KMCR, named SP-KMCR. Finally, a fault-tolerant multicast routing algorithm (FTSP-KMCR) that based on SP-KMCR is presented.

- In Chapter 6, we present the system architecture. We then describe its two main components that are a spiking neural processing core (SNPC) as a main computational unit and a 3D router where the proposed spike routing algorithms are implemented. Furthermore, some aspects of deploying the applications onto the system are also presented.

- We dedicate Chapter 7 for presenting implementation, evaluation, and results. We first describe how to implement and evaluate the proposed architecture and algorithms. After that, we provide a comprehensive evaluation and results of the proposed works.

- Finally in Chapter 8, we end this thesis with the conclusion before discussing further future works.

## 2

# Neural Network Architecture: Background

N THIS CHAPTER, we first present an overview of the artificial neural network, its generations, and topologies. After that, we introduce implementations of the artificial neural network and also spiking neural network, in

each of which we consider the neuron model, learning, and existing implementations.

#### 2.1 Neural Network

#### Overview

A coarse biological neuron, shown in Figure 2.1 (a) is considered to be an information processing system. *Dendrites* play a role as input devices, where input signals are collected. The neuron will process the signals and then produce output signals which are propagated along its *axon*. Finally, the axon transmits the signals via synapses to dendrites of other neurons. It is important to emphasize that this model of a biological neuron is very coarse, and there are many different types of neurons, each of which has different properties.

Figure 2.1: (a) a cartoon drawing of a biological neuron (b) a mathematical model of a neuron.

In the computational model of a neuron, shown in Figure 2.1 (b), each output signal (e.g.,  $x_0$ ) from a previous neuron is multiplied with a weight (e.g.,  $w_0$ ). This weight presents the synaptic strength at that synapse. Dendrites carry the signals (e.g.,  $w_0x_0$ ) to the cell body where they all get summed. In the basic model, if the final sum exceeds a certain threshold, the neuron can *fire*, sending a spike along its axon. An activation function is modeled as the *firing rate* of the neuron.

Figure 2.2: Generations of artificial neural network.

Neural networks can be classified into three generations according to their computation units [28, 29], as shown in Figure 2.2:

- The first generation: networks have neurons as computational units, and these neurons are referred to as perceptrons or threshold gates. These networks only process with digital inputs and outputs, boolean functions, and a single hidden layer. Multilayer perceptrons, Hopfield networks, and Boltzmann machines are typical examples of this kind of neural network.

- The second generation: each neuron in the network applies an activation function with a continuous set of possible output values, such as sigmoid or polynomial or exponential functions. Feedforward, recurrent sigmoidal neural networks, and radial basis function units are considered typical examples of this generation. Moreover, these systems compute not only arbitrary boolean functions but also functions with analog inputs and outputs. Furthermore, neural networks in this generation support learning algorithms based on gradient descent.

- The third generation: Spiking neural networks are considered to be a closer approach to modeling biological neurons than previous ANNs. Biological neural systems use the timing of single-action potentials (or spikes) to encode information. Basically, each spiking neuron has a membrane potential which is integrated by incoming pikes. When the membrane potential exceeds a threshold, the neuron fires (i.e., a spike is generated).

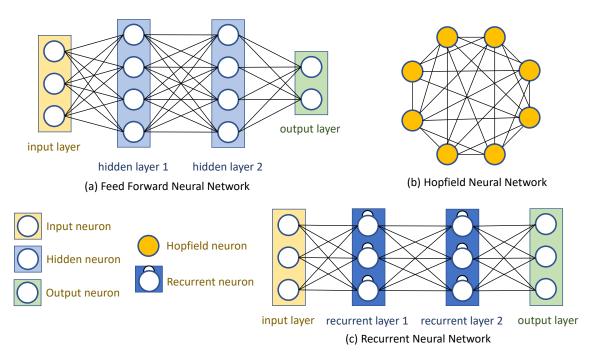

Figure 2.3: Some common neural network topologies.

#### NEURAL NETWORK TOPOLOGIES

Neurons can be connected together in different manners. Typical neural network topologies are summarized, as illustrated in Figure 2.3:

• Feed forward neural networks: Figure 2.3 (a) depicts a feed forward neural network (FF or FFNN). This network is organized into separate layers of neurons: input, hidden, and output layers. In this architecture, there are many connections between neurons across layers, but not within a layer. Information is fed from the front to the back. This network usually is used with the back-propagation training method. There are some other neural networks with the same topology as FFNNs. If neurons use a simple binary function, this architecture is called *Perceptron (B)* or *Multilayer perceptron (MLP)*. The simplest network, with two input neurons and one output neuron, can be used to model logic gates. *Radial basis function (RBF)* [30] networks are FFNNs with neurons having radial basis functions. RBFs are suitable for pattern recognition and classification.

- Hopfield neural network (HFs): HFs [31] are quite different compared to the systems mentioned above, as shown in Figure 2.3 (b). In this architecture, each neuron is connected to others. Neurons play distinct roles when the network is trained, they are input, hidden, and output, corresponding to before, during, and after training respectively. HFs offer a model for understanding human memory. They are also used as content-addressable memories. *Boltzmann machines (BMs)* [32] are pretty similar to HFs. However, BMs are composed of some input neurons, while the others are hidden neurons. The input neurons will become output neurons after each update of the full network.

- Recurrent neural networks (RNNs): As shown in Figure 2.3 (c), RNNs are pretty similar to FFNNs, but the hidden layers are replaced by recurrent neural layers. Unlike FFNNs, neurons in RNNs are not only fed from the previous layer but also from the previous pass of themselves [33]. This results in different outputs when changing the order of information in feeding. RNNs can be used in many areas where the data form can be represented as a sequence such as a string of text. Thus, RNNs are regularly used in autocompletion systems and machine translation. A big drawback of RNNs is the vanishing/exploding problem when using gradient descent technique.

#### 2.2 Artificial Neural Network

#### 2.2.1 Learning Rules

One of the major challenges for neuromorphic designs is how to implement learning algorithms. In general, implementation of learning algorithm can be performed on-chip or off-chip depending on many factors such as neural network models and hardware resources.

#### Supervised Learning

Backpropagation (BP), a supervised learning method, is the most commonly used algorithm for programming neuromorphic systems. It can be employed in many neural network models such as feed-forward neural networks, recurrent neural networks, and convolution neural networks. The simple way to implement BP in hardware is off-chip [34, 35]. In this case, PB is performed on a traditional host machine. After that, pre-trained parameters are transferred or configured into the target neuromorphic chip. While this method benefits for taking precision of software implementation and requiring lower hardware resource, it is not suitable for systems that have to re-train frequently. However, on-chip BP implementations have been used in many neuromorphic systems [36, 37]. Besides, variations of BP that are optimized or simplified for neuromorphic systems are also implemented [38, 39]. There are other on-chip learning implementations for convolution neural networks [40, 41], Boltzmann machines [42], Restricted Boltzmann machines [43] and deep belief networks [44].

#### Unsupervised Learning

Compared to supervised learning, implementations of unsupervised learning are less popular. There have been some on-chip ones implemented in neuromorphic systems. Most of them were based on self-organizing maps or self-organizing learning rules [45–47].

#### 2.2.2 Fundamental Implementation

For ANN neurons, the inputs, weights, and outputs are presented as real values. In general, implementations of ANN neurons can be categorized in two ways: analog and digital. Analog implementations offer power efficiency with low area cost and high processing speed, but their downside is a limited accuracy due to being susceptible to noise and difficulty in presenting real values. On the other hand, digital implementations benefit high computation precision, high reliability, and programmability, but they suffer high area cost and high latency compared to analog approaches.

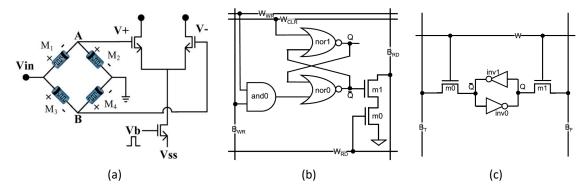

Figure 2.4: Synapse implementation: (a) Analog: memristor bridge synaptic circuit [48]. Digital: (b) 12T scheduler SRAM Cell (simplified) (c) 6T core SRAM cell [16].

Digital neuron implementations are relatively straightforward thanks to supporting powerful design tools. Also, synaptic strengths (weights) are implemented by using registers, latches, or SRAM (see Figure 2.4(b-c)). In addition, all elementary operations such as adders, subtracters, and multipliers can be implemented by available standard circuits [49] while implementation of non-linear activation functions such as sigmoid use specialized hardware, approximated mechanisms (i.e., piecewise-linear function) [35], or look-up tables [50].

Apart from digital CMOS technologies, FPGAs are very attractive due to its programmability and short development time. An FPGA implementation for a general-purpose neuron is presented in [51]. In [52], authors discussed how to implement a single neuron with parallel computation blocks, in addition to bit precision and use of look-up table. Other attractive works were presented in [53, 54]. In these works, authors also discussed implementations and optimization methods of arithmetic operations on FPGAs such as shift add neural arithmetic for fast perceptron and non-linear activation functions.

Analog neuron implementations: In the analog domain, weights are usually implemented by using registers [55], charge-coupled devices [56], capacitors [57, 58], floating gate EEP-ROMS [59], or memristor in recent years (see Figure 2.4(a)). For non-linear activation functions, the characteristic can sometimes be captured directly or using some approximation functions [60]. Although it is difficult to implement a coherent set of all

Table 2.1: Platform comparison for neuromorphic implementation [62].

|               | Parallel | FPNN | DSP | FPGA | Analog | Digital |

|---------------|----------|------|-----|------|--------|---------|

|               | com-     | in   |     |      | ASIC   | ASIC    |

|               | puter    | FPGA |     |      |        |         |

| Speed<br>Area | +        | +    | -   | +    | +++    | ++      |

| Area          |          | +    | _   | +    | +++    | ++      |

| Cost          |          | ++   | ++  | ++   |        |         |

| Design time   | +        | +++  | ++  | ++   |        |         |

| Reliability   | ++       | ++   | ++  | ++   |        | +       |

<sup>- -</sup> very unfavorable, - unfavorable

the basic elements, some operations can be easy to achieve by exploiting simple physical effects [61], such as accumulator can be presented by summing currents (Kirchhoff's current law). Table 2.1 compares different platforms for hardware implementation of neural networks.

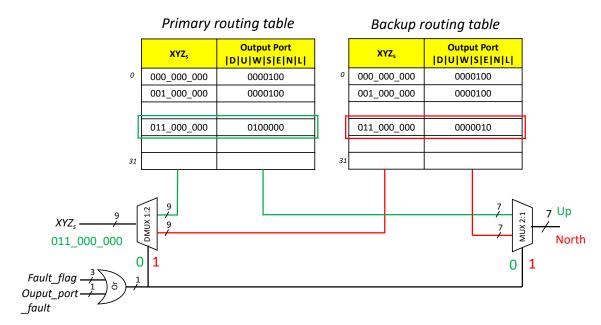

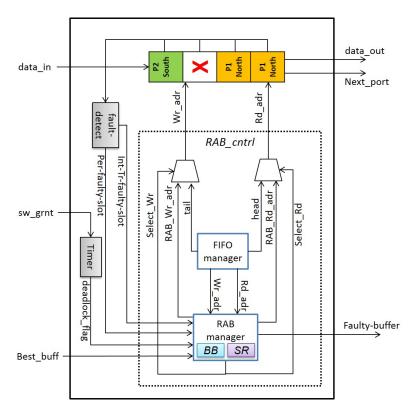

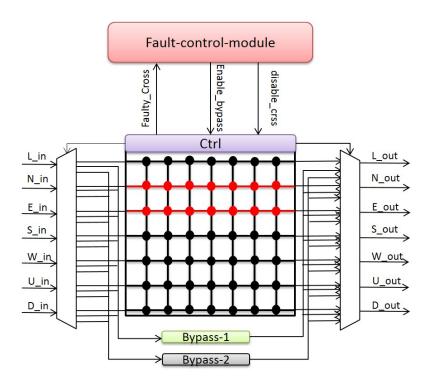

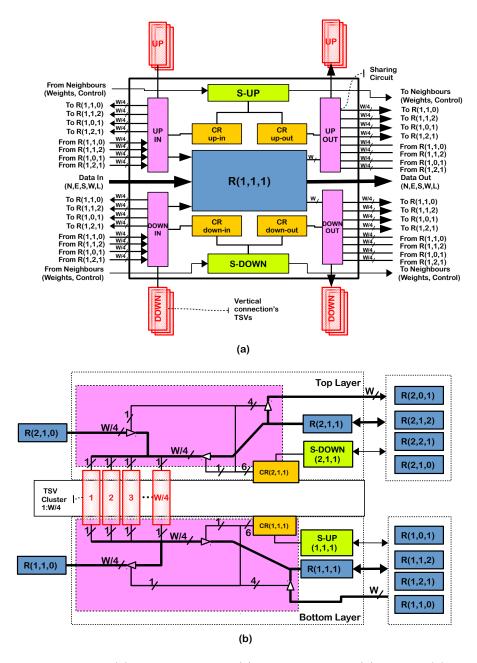

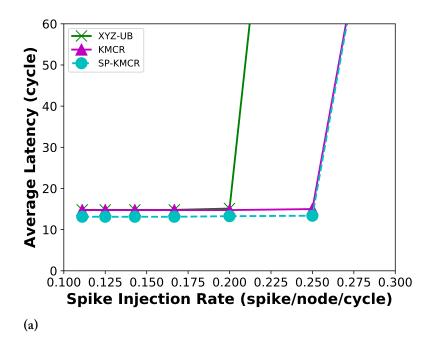

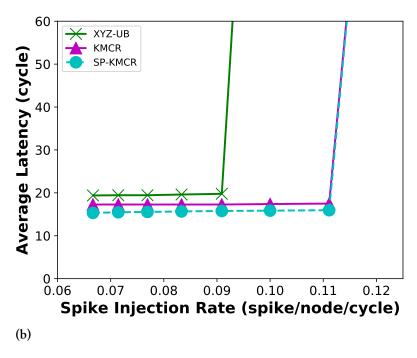

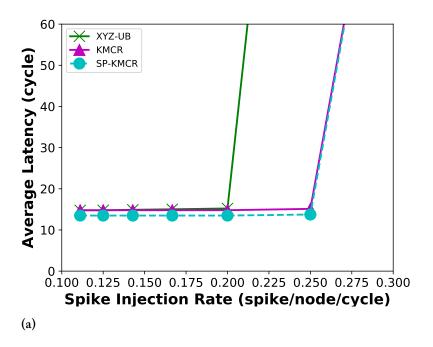

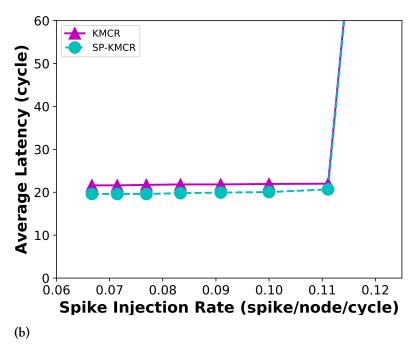

#### 2.2.3 Existing Architectures