## Adaptive Systems Laboratory Research Introduction

Adaptive Systems Laboratory, Division of Computer Engineering School of Computer Science and Engineering University of Aizu, Aizu-Wakamatsu City 965-8580.

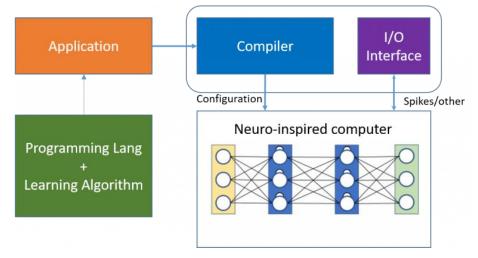

ASL focuses on energy-efficient adaptive computing systems based on neuronal algorithms and fault-tolerant scalable interconnects to overcome the limitation of traditional stored-program computing style. In particular, we are investigating the computational properties of neural processing systems by developing new chips and systems that emulate the principles of computation in the neural systems. Our applications range from neuro-inspired (brain-like) low-power computing embedded systems to adaptive neural-based control, and brain-machine interfaces.

Currently, we are investigating the following two main related research areas:

## Adaptive Neuro-inspired Computing Systems and Platforms

The biological brain implements parallel computations using a complex structure that is different from the conventional stored-program computing style. Our brain is a low-power, fault-tolerant, and high-performance machine! It consumes only about 20W and brain circuits continue to operate as the organism needs even when the circuit (neuron, neuroglia, etc.) is perturbed or died. Computations in neural networks are naturally parallel and distributed among billion neurons. This very high degree of distributed parallelism with the continuous advances in

neuro-inspired engineering and neuroinformatics will enable the development and manufacture of low-clock frequency (low-power) and high-throughput neuro-inspired computing architectures and systems.

Hardware implementations of neural networks are very efficient and effective methods to provide cognitive functions on a chip compared with conventional stored-program computers/processors. One of the most difficult of the challenges in modeling the brain is the massive interconnectivity. So, the challenges that need to be solved include building a small-size massively parallel architecture with scalable interconnects, low-power consumption, and reliable circuits.

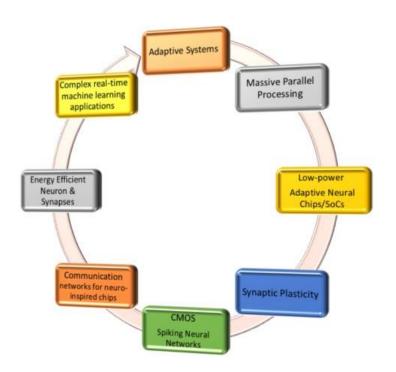

Our focus is to investigate novel neuro-inspired computing systems and adaptive low-power neural chips/SoCs able to scale up to biological levels. Currently, we are studying the following topics:

- Neuro-inspired neural network models and computing methods

- Low-power adaptive neural chips

- Spiking neural architecture building blocks

- Conventional hardware (i.e. VLSI, FPGAs) and innovative hardware (i.e., memristor) implementation of Neuro-inspired systems

- Synaptic and structural plasticity circuit emulations

- Reliable and scalable communication networks for neuro-inspired chips/systems;

- Neural circuits, models for neurons and synapses

- Ultra-low power biological-scale neurons

- Reconfigurability and adaptability methods

- On-chip learning algorithms

## Energy-efficient Fault-tolerant Scalable Interconnects

Future computing systems would contain hundreds of components made of processor cores, DSPs, memory, accelerators, and I/O all integrated into a single die area of just a few square millimeters. Such "tiny" complex system would be interconnected via a novel on-chip

interconnect closer to a sophisticated network than to current bus-based solutions. This network must provide high throughput, low latency, and also fault-tolerance while keeping area and power consumption low. Three-dimensional Networks-on-Chip (3D-NoC) is an auspicious solution to alleviate the interconnect bottleneck and reduce the power consumption in current System-on-Chips (SoCs) designs. However, 3D-NoC systems are becoming susceptible to a variety of faults caused by crosstalk, the impact of radiations, oxide breakdown, and so on. As a result, a simple failure in a single transistor caused by one of these factors may compromise the entire system reliability where the failure can be illustrated in corrupted message delivery, time requirement unsatisfactory, or even sometimes the whole system collapse.

Our research effort in this area is about solving several design challenges to enable the packetswitched and other novel switching schemes for networks of massively parallel cores in conventional load/store and in a novel neuro-inspired computing systems. We are currently investigating the following topics: Low-power interconnects for an event-driven large network of neuromorphic cores; Implementation techniques for TSV based NoCs; 3D-IC integration; Fault-tolerant and reliability issues; New topologies and flow-control methods; Photonic Interconnects; Organic circuits.

## References

- 1. Abderazek Ben Abdallah, "Neuro-inspired Computing Systems & Applications", Keynote Speech, 2018 International Conference on Intelligent Autonomous Systems (ICoIAS'2018), March 1-3, 2018, Singapore.

- 2. The H. Vu, Ryunosuke Murakami, Yuichi Okuyama, Abderazek Ben Abdallah, "Efficient Optimization and Hardware Acceleration of CNNs towards the Design of a Scalable Neuro-inspired Architecture in Hardware", Proc. of the IEEE International Conference on Big Data and Smart Computing (BigComp-2018), January 15-18, 2018. [paper.pdf], [slides.pdf]

- 3. Ryunosuke Murakami, Yuichi Okuyama, Abderazek Ben Abdallah, "Animal Recognition and Identification with Deep Convolutional Neural Networks for Farm Monitoring", Information Processing Society Tohoku Branch Conference, Feb. 10, 2018 [slides.pdf]

- 4. Yuji Murakami, Yuichi Okuyama, Abderazek Ben Abdallah, "SRAM Based Neural Network System for Traffic-Light Recognition in Autonomous Vehicles", Information Processing Society Tohoku Branch Conference, Feb. 10, 2018. [slides.pdf]

- 5. Kanta Suzuki, Yuichi Okuyama, Abderazek Ben Abdallah, "Hardware Design of a Leaky Integrate and Fire Neuron Core Towards the Design of a Low-power Neuro-inspired Spike-based Multicore SoC", Information Processing Society Tohoku Branch Conference, Feb. 10, 2018. [slides.pdf]

- Khanh N. Dang, Abderazek Ben Abdallah, "Architecture and Design Methodology for Highly-Reliable TSV-NoC Systems", Invited Book Chapter, <u>Nova Science Publishers</u>, Feb. 2018, ISBN: 978-1-53613-327-12018. [preprint.pdf]

- 7. Khanh N. Dang, Akram Ben Ahmed, Yuichi Okuyama, and Abderazek Ben Abdallah, "<u>Scalable Design Methodology and Online Algorithm for TSV-cluster Defects Recovery in Highly Reliable 3D-NoC Systems</u>", IEEE Transactions on Emerging Topics in Computing, 2017 (in press). DOI: 10.1109/TETC.2017.2762407. [preprint.pdf]

- Abderazek Ben Abdallah, Khanh N. Dang, Yuichi Okuyama, <u>"A Low-overhead Fault tolerant Technique</u> for TSV-based Interconnects in 3D-IC Systems", The 18th International Conference on Sciences and Techniques of Automatic control and computer engineering (STA'2017), December 21-23, 2017. [paper.pdf], [slides.pdf]

- Achraf Ben Ahmed, Tsutomu Yoshinaga, Abderazek Ben Abdallah, "<u>Scalable Photonic Networks-on-Chip</u> <u>Architecture Based on a Novel Wavelength-Shifting Mechanism</u>", IEEE Transactions on Emerging Topics in Computing, 2017 (in press). DOI: <u>10.1109/TETC.2017.2737016</u>

- Khanh N. Dang, Akram Ben Ahmed, Xuan-Tu Tran, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>A</u> <u>Comprehensive Reliability Assessment of Fault-Resilient Network-on-Chip Using Analytical Model</u>", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 25, Issue: 11, pp. 3099 – 3112, Nov. 2017. DOI:10.1109/TVLSI.2017.2736004. [preprint.pdf]

- 11. Abderazek Ben Abdallah, "<u>Neuro-Inspired Adaptive Manycore SoCs and Applications</u>", Keynote Speech, International Conference on Control, Automation and Robotics, April 22-24, 2017, Nagoya, Japan.

- Book: Abderazek Ben Abdallah (Author), <u>"Advanced Multicore Systems On-Chip: Architecture, On-Chip</u> <u>Network, Design</u>", Publishers: Springer; 1st ed, 2017, ISBN-13: 978-9811060915, ISBN-10: 98110609162017.

- Khanh N. Dang, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>A Low-overhead Soft-Hard Fault Tolerant Architecture, Design, and Management Scheme for Reliable High-performance Many-core</u> <u>3D-NoC Systems</u>", Journal of Supercomputing, Volume 73, Issue 6, pp 2705–2729, 2017. doi:10.1007/s11227-016-1951-0 [Springer Nature (.pdf)]

- 14. Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>Microring Fault-resilient Photonic Network-on-Chip for Reliable High-performance Many-core Systems</u>", Journal of Supercomputing, Volume 73, <u>Issue 4</u>, pp 1567–1599, April 2017.doi: 10.1007/s11227-016-1846-0. [<u>Springer Nature (.pdf)</u>]

- 15. Abderazek Ben Abdallah, "<u>Adaptive SoCs for Smart Autonomous Systems</u>", Keynote Speech, 17th International Conference on Sciences and Techniques of Automatic control & Computer Engineering (STA2016), Sousse, December 19-21, 2016. [slides.pdf], [BibTex]

- Khanh N. Dang, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>Reliability Assessment and Quantitative Evaluation of Soft-Error Resilient 3D NoC System</u>", Prof. of the 25th-IEEE Asian Test Symposium (ATS'16), Hiroshima, November 21-24, 2016. [slides.pdf], [BibTex]

- 17. Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>A Power Estimation Method for Mesh-based</u> <u>Photonic NoC Routing Algorithms</u>", Proc. of the Fourth International Symposium on Computing and Networking, Hiroshima, pp. 452-453, November 22-25, 2016. [BibTex]

- Khanh N. Dang, Yuichi Okuyama, Abderazek Ben Abdallah, "<u>Soft-Error Resilient Network-on-Chip for Safety-Critical Applications</u>", 2016 IEEE International Conference on Integrated Circuit Design and Technology (ICICDT), Ho Chi Minh, June 27 29, 2016. [slides.pdf], [BibTex]

- 19. Akram Ben Ahmed, Abderazek Ben Abdallah, "<u>Adaptive fault-tolerant architecture and routing algorithm</u> <u>for reliable many-core 3D-NoC systems</u>", Journal of Parallel and Distributed Computing, Volumes 93–94, July 2016, Pages 30-43, ISSN 0743-7315, doi:10.1016/j.jpdc.2016.03.014. [preprint.pdf], [BibTex]

- 20. Achraf Ben Ahmed, Abderazek Ben Abdallah, <u>"An Energy-efficient High-throughput Mesh-based</u> <u>Phototonic On-chip Interconnect for Many-core Systems</u>", Photonics, 2016; 3(2):15. doi:10.3390/photonics3020015. [paper.pdf], [BibTex]

- Khanh N. Dang, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, Xuan-Tu Tran, "<u>Soft-Error</u> <u>Resilient 3D Network-on-Chip Router</u>", Proc. of IEEE 7th International Conference on Awareness Science and Technology (iCAST 2015), pp. 84 – 90, Sep. 22-24, 2015. [BibTex]

- 22. Achraf Ben Ahmed, Abderazek Ben Abdallah, "<u>Hybrid Silicon-Photonic Network-on-Chip for Future</u> <u>Generations of High-performance Many-core Systems</u>," Journal of Supercomputing, Dec. 2015, Vol. 71, Issue 12, pp 4446-4475. [preprint.pdf]. [BibTex]

- 23. Michael Meyer, Akram Ben Ahmed, Yuki Tanaka, Abderazek Ben Abdallah, "On the Design of a Faulttolerant Photonic Network-on-Chip," Proc. of IEEE International Conference on Systems, Man, and Cybernetics (SMC2015), Oct. 9-12, 2015, pp. 821 – 826. [BibTex]

- Michael Meyer, Akram Ben Ahmed, Yuichi Okuyama, Abderazek Ben Abdallah, <u>"FTTDOR: Microring Fault-resilient Optical Router for Reliable Network-on-Chip Systems</u>", Proc. of IEEE 9th International Symposium on Embedded Multicore/Many-core SoCs (MCSoC-15), pp. 227 234, Sep 23-25, 2015. [BibTex]

- Achraf Ben Ahmed, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, <u>"Hybrid Photonic NoC based on Non-blocking Photonic Switch and Light-weight Electronic Router"</u>, Proc. of IEEE International Conference on Systems, Man, and Cybernetics (SMC2015), pp. 56 61, Oct. 9-12, 2015. [BibTex]

- Achraf Ben Ahmed, Yuichi Okuyama, Abderazek Ben Abdallah, <u>"Contention-free Routing for Hybrid Photonic Mesh-based Network-on-Chip Systems"</u>, Proc. of IEEE 9th International Symposium on Embedded Multicore/Many-core SoCs (MCSoC-15), pp. 235 242, Sep 23-25, 2015. [BibTex]

- Abderazek Ben Abdallah, Mitsuhiro Nakamura, Akram Ben Ahmed, Michael Meyer, Yuichi Okuyama, <u>"Fault-tolerant Router for Highly-reliable Many-core 3D-NoC Systems"</u>, Proc. of the 3rd International Scientific Conference on Engineering and Applied Sciences (ISCEAS 2015), July 29-31, 2015, Okinawa, Japan. [BibTex]

- Ben Ahmed, Ashraf; Okuyama, Yuichi; Ben Abdallah, Abderazek, "Non-blocking electro-optic network-onchip router for high-throughput and low-power many-core systems," in Information Technology and Computer Applications Congress (WCITCA), 2015 World Congress on, vol., no., pp.1-7, 11-13 June 2015 doi: 10.1109/WCITCA.2015.7367068

- Achraf Ben Ahmed, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah,"Efficient Router Architecture, Design and Performance Exploration for Many-core Hybrid Photonic Network-on-Chip (2D-PHENIC)", Proc. of the International Conference on Information Science and Control Engineering, pp. 202 – 206, April 24-26, 2015.

- Ben Ahmed, M. Meyer, Y. Okuyama, and A. Ben Abdallah, "Adaptive Error- and Traffic Aware Router Architecture for 3D Network-on-Chip Systems", IEEE Proceedings of the 8th International Symposium on Embedded Multicore/Many-core SoCs (MCSoC-14), pp. 197-2014, Sept. 2014.

- Ben Ahmed, A. Ben Abdallah, "OASIS 3D-Router Hardware Physical Design", Technical Report, Adaptive Systems Laboratory, Division of Computer Engineering, School of Computer Science and Engineering, University of Aizu, July 8, 2014.

- 32. Ben Ahmed, A. Ben Abdallah, "Graceful Deadlock-Free Fault-Tolerant Routing Algorithm for 3D Networkon-Chip Architectures", Journal of Parallel and Distributed Computing, 74/4 (2014), pp. 2229-2240.

- 33. Achraf Ben Ahmed, A. Ben Abdallah, "Architecture and Design of Real-Time System for Elderly Health Monitoring", Journal of Embedded Systems, 2014.

- Ben Ahmed, A. Ben Abdallah, "PHENIC: Towards Photonic 3D-Network-on-Chip Architecture for Highthroughput Many-core Systems-on-Chip", IEEE Proc. of the 14th Int. Conf. on Sciences and Techniques of Automatic Control and Computer Eng., Dec. 2013.

- 35. Akram Ben Ahmed, Achraf Ben Ahmed, A. Ben Abdallah, "Deadlock-Recovery Support for Fault-tolerant Routing Algorithms in 3D-NoC Architectures", IEEE Proceedings of the 7th International Symposium on Embedded Multicore/Many-core SoCs (MCSoC-13), pp. 67-72, 2013.

- Akram Ben Ahmed, A. Ben Abdallah, "Architecture and Design of High-throughput, Low-latency and Fault Tolerant Routing Algorithm for 3D-Network-on-Chip", The Jnl. of Supercomputing, December 2013, Volume 66, Issue 3, pp 1507-1532.

- Achraf Ben Ahmed, A. Ben Abdallah, "Hardware/Software Prototyping of Dependable Real-Time System for Elderly Health Monitoring", IEEE Proc. of the World Congress on Computer and IT (ICMAES), June 2013.

- Akram Ben Ahmed, T. Ouchi, S. Miura, A. Ben Abdallah, "Run-Time Monitoring Mechanism for Efficient Design of Application-specific NoC Architectures in Multi/Manycore Era", IEEE Proc. of the 6th International Workshop on Engineering Parallel and Multicore Systems (ePaMuS2013), July 2013.

- 39. Ben Abdallah, "Towards the Development of Smart Multicore Bio-Chip for Body-Area Networks ", Invited tak, IEEE-PCSJ Conference, November 2, 2013.

- Ben Abdallah, "PHENIC: Silicon Photonic 3D-Network-on-Chip Architecture for High-performance Heterogeneous Many-core System-on-Chip ", Technical Report, Adaptive Systems Laboratory, The University of AizuRef. PTR0901A0715-2013, Sept. 013.

- 41. Achraf Ben Ahmed, "Interactive Real-time Interface for Smart Remote Health Monitoring and Analysis ", Master's Thesis, Graduate School of Computer Science and Engineering, The University of Aizu, Feb. 2013.

- 42. Kenichi Mori, "OASIS Network-on-Chip Prototyping on FPGA ", Master's Thesis, The University of Aizu, Feb. 2012.

- 43. Akram Ben Ahmed, "On the Design of a 3D Network-on-Chip for Many-core SoC ", Master's Thesis, The University of Aizu, Feb. 2012.

- 44. Akram Ben Ahmed, A. Ben Abdallah, "On the Design of a 3D Network-on-Chip for Many-core SoC ", Technical Report, The University of Aizu, Feb. 2012.

- 45. Akram Ben Ahmed, A. Ben Abdallah, "Low-overhead Routing Algorithm for 3D Network-on-Chip", IEEE Proc. of the The Third International Conference on Networking and Computing (ICNC'12), pp. 23-32, 2012.

- 46. Akram Ben Ahmed, A. Ben Abdallah, "LA-XYZ: Low Latency, High Throughput Look-Ahead Routing Algorithm for 3D Network-on-Chip (3D-NoC) Architecture ", IEEE Proceedings of the 6th International Symposium on Embedded Multicore SoCs (MCSoC-12), pp. 167-174, 2012.

- Achraf Ben Ahmed, Yumiko Kimezawa, A. Ben Abdallah, "Towards Smart Health Monitoring System for Elderly People ", IEEE Proceedings of The 4th International Conference on Awareness Science and Technology (iCAST 2012), pp. 248-253, 2012.

- Akram Ben Ahmed, A. Ben Abdallah, "ONoC-SPL Customized Network-on-Chip (NoC) Architecture and Prototyping for Data-intensive Computation Applications ", IEEE Proceedings of The 4th International Conference on Awareness Science and Technology (iCAST 2012), pp. 257-262, 2012.

- 49. Ryuya Okada, "Architecture and Design of Core Network Interface for Distributed Routing in OASIS NoC", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2012.

- 50. Tomotaka Kasahara, "Performance and Complexity Study of Multi-QueueCore Systems", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2012.

- 51. R. Okada, "Architecture and Design of Core Network Interface for Distributed Routing in OASIS NoC", Technical Report, Adaptive Systems Lab, The University of Aizu, Feb., 2012.

- 52. Ben Abdallah, et al., "Natural Instruction Level Parallelism-aware Compiler for High-Performance QueueCore Processor Architecture", Journal of Supercomputing, Vol. 57, No. 3 (2011), pp. 314-338.

- Hiroki Hoshino, "Development of Parallel Queue Processor Architecture and its Integrated Development Environment", Master's Thesis, Graduate School of Computer Science and Engineering, The University of Aizu, Feb. 2011.

- Taichi Maekawa, "Design and Evaluation of Dual Mode Processor Architecture", Master's Thesis, Graduate School of Computer Science and Engineering, The University of Aizu, Feb. 2011.

- Masashi Masuda, "Produced Order Queue Compiler Design", Master's Thesis, Graduate School of Computer Science and Engineering, The University of Aizu, Feb. 2011.

- 56. Takahiro Uesaka, "OASIS NoC Topology Optimization with ShortPath Link", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2011.

- 57. Shunichi Kato, "Shared Memory MultiQueueCore Processor Design", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2011, Ref. 10SK-GT10.

- 58. Yumiko Kimezawa, "Multicore SoC Architecture for Realtime Data Intensive ECG Processing", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2011.

- Akram Ben Ahmed, A. Ben Abdallah, K. Kuroda, Architecture and Design of Efficient 3D Network-on-Chip (3D NoC) for Custom Multicore SoCs, IEEE Proc. of the 5th International Conference on Broadband, Wireless Computing, Communication and Applications (BWCCA-2010), Nov. 2010.

- K. Mori, A. Esch, A. Ben Abdallah, K. Kuroda, Advanced Design Issues for OASIS Network-on-Chip Architecture, IEEE Proc. of the 5th International Conference on Broadband, Wireless Computing, Communication and Applications (BWCCA-2010), Nov. 2010, pp. 74-79.

- 61. Ben Abdallah, Efficient Parallel ECG Processing Algorithm and Design of Flexible Health Monitoring System for Elderly People, Innovation Research Journal, March 2010, pp. 24-27.

- Ben Abdallah, Y. Haga, K. Kuroda, "An Efficient Algorithm and Embedded Multicore Implementation for ECG Analysis in Multi-lead Electrocardiogram Records", IEEE Proc. of the 39th he International Conference on Parallel Processing Workshop, San Diego, pp.99-103, Sept. 13-16, 2010.

- 63. Yuuki Omoto, "Development Environment for Single Chip Computer intended for Queue Computing Development and Education", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2010.

- 64. Haga Yasuyoshi, "Architecture and Design of Application Specific Multicore SoC", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2010.

- 65. Reo Honjoya, "Development of User Friendly Assembler for Queue Computers", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2010.

- 66. Mori Kenichi, "Optimizations Techniques and FPGA Prototyping of OASIS Network-on-Chip", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2010.

- 67. Miura Shohei, "Architecture and Design of Parameterizable Network-on-Chip", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2010.

- Y. Haga, A. Ben Abdallah, and K. Kuroda, "Embedded MCSoC Architecture and Period-Peak Detection (PPD) Algorithm for ECG/EKG Processing", 'The 19th Intelligent System Symposium (FAN 2009), pp.298-303, Sep. 2009.

- 69. S. Miura, A. Ben Abdallah, and K. Kuroda, "PNoC Design and Preliminary Evaluation of a Parameterizable NoC for MCSoC Generation and Design Space Exploration", The 19th Intelligent System Symposium (FAN 2009), pp.314-317, Sep. 2009.

- K. Mori, A. Ben Abdallah, and K. Kuroda, "Design and Evaluation of a Complexity Effective Network-on-Chip Architecture on FPGA", The 19th Intelligent System Symposium (FAN 2009), pp.318-321, Sep. 2009.

- M. Masuda, A. Canedo, A. Ben Abdallah, "Efficient Code Generation Algorithm for Natural Instruction Level Parallelism-aware Queue Architecture", The 19th Intelligent System Symposium (FAN 2009), pp.308-313, Sep. 2009.

- 72. Canedo, A. Ben Abdallah, and M. Sowa, "Efficient Compilation for Queue Size Constrained Queue Processors", The Journal of Parallel Computing, Vol.35, pp. 213-225, 2009.

- Canedo, A. Ben Abdallah, and M. Sowa, "Compiler Support for Code Size Reduction using a Queue-based Processor", Transactions on High-Performance Embedded Architectures and Compilers, Vol. 2, Issue 4, pp. 269-285, 2009.

- 74. Shohei Miura, Abderazek Ben Abdallah, Kenichi Kuroda, "設計空間探索と MCSoC の生成に適している parameterizable NoC (PNoC)のハードウェア設計と事前評価", 第 34 回パルテノン研究会, pp.105-108, Aug. 2009.

- 75. Masashi Masuda, "Graph Transformation Methods and Theoretical Performance Evaluation of Queue Computation Models ", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2009.

- Hiroki Hoshino, "Advanced Hardware Optimization Algorithms for High Performance Queue Processor Architecture ", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2009.

- 77. Tachi Maekawa, "Research on Hardware Design of Dual-Mode Processor Architecture", Bachelor Thesis, School of Computer Science and Engineering, The University of Aizu, Feb. 2009.

- A Canedo, A. Ben Abdallah, M Sowa, "Design and implementation of a queue compiler", Jnl of Microprocessors and Microsystems 33 (2), pp.129-138, 2009.

- Masashi Masuda, A Ben Abdallah, Arquimedes Canedo, "Software and Hardware Design Issues for Low Complexity High Performance Processor Architecture", IEEE Prof. of the Int. COnference of Parallel Processing Workshops, pp. 558-565, 2009.

- Ben Abdallah, A. Canedo, T. Yoshinga, and M. Sowa, The QC-2 Parallel Queue Processor Architecture, Journal of Parallel and Distributed Computing, Vol. 68, No. 2, pp. 235-245, 2008.

- T. Maekawa, A. Ben Abdallah, and K. Kuroda, "Single Instruction Dual-Execution Model Processor Architecture", Proc. IEEE/IFIP Int'l Conf. on Embedded and Ubiquitous Computing (EUC2008), pp.30-36, Dec. 2008.

- 82. H. Hoshino, A. Ben Abdallah, and K. Kuroda, "Advanced Optimization and Design Issues of a 32-bit Embedded Processor Based on Produced Order Queue Computation Model", IEEE/IFIP Int'l Conf. on Embedded and Ubiquitous Computing (EUC2008),pp.16-22, Dec.2008.

- Canedo, A. Ben Abdallah, and M. Sowa, "Quantitative Evaluation of Common Subexpression Elimination on Queue Machines", Proc. IEEE Int'l Sym. on Parallel Architectures, Algorithms, and Networks (I-SPAN 2008), pp.25-30. 2008.

- Ben Abdallah, et. all, "Processor for Mobile Applications", ISBN: 978-1-60566-046-2, IGI Publishers, 2008.

- M. Akanda, A. Ben Abdallah, and M. Sowa, "Dual-Execution Mode Processor Architecture", Journal of Supercomputing, Vol. 44, No. 2, pp. 103-125, 2008.

- 86. M. Sowa. et all. "Queue Machines for Next Generation Computer Systems", Proc. of The International Workshop on Modern Science and Technology (IWMST), 2008.

- 87. Canedo, Ben Abdallh Abderazek, and Masahiro Sowa, "Compiling for Reduced Bit-Width Queue Processors", Journal of Signal Processing Systems, Volume 59, Issue 1, pp 45-55, 2010.

- Canedo, A. Ben Abdallah, and M. Sowa, "A New Code Generation Algorithm for 2-offset Producer Order Queue Computation Model", Journal of Computer Languages, Systems & Structures, Vol. 34, Issue 4, pp. 184-194, 2007.

- 89. Ben Abdallah, and M. Sowa, "Advanced Power Management Techniques for Mobile Communication Systems", Journal of Computer Research, Vol. 14, No.2, pp. 109-128, 2007.

- Mushiq Akanda, A. Ben Abdallah, and M. Sowa, "Dual-Execution Mode Processor Architecture for Embedded Applications", Journal of Mobile Multimedia, Vol. 3, No. 4, pp. 347-370, 2007.

- 91. Y. Nakanishi, A. Canedo, A. Ben Abdallah, and M. Sowa, "Optimizing Reaching Definitions Overhead in Queue Processors", Journal of Convergence Information technology, 2007, Vol. 2, No. 4, pp. 36-40, 2007.

- Ben Abdallah, and M. Sowa, "Efficient Design Methodology and Synthesizable Core for Multicore SoCs", ISBN: 978-81-7895-258-1, Signpost Publishers, 2007.

- Ben Abdallah, and M. Sowa, "Buffer Design in Packet Switched Networks for MCSoCs Applications", ISBN: 978-81-7895-258-1, Signpost Publishers, 2007.

- Ben Abdallah, and M. Sowa, "Power Optimization techniques for Mobile Multicore SoCs", ISBN: 978-81-7895-258-1, Signpost Publishers, 2007.

- 95. Canedo, A. Ben Abdallah, M. Sowa, New Code Generation Algorithm for QueueCore An Embedded Processor with High ILP, IEEE Proc of the Eighth International Conference on Parallel and Distributed Computing, Applications and Technologies, 185-192, 2007.

- 96. Ben Abdallah, T Yoshinaga, and M. Sowa, "Mathematical Model for Multiobjective Synthesis of NoC Architectures", IEEE Proc. of the 36th International Conference on Parallel Processing, Sept., 2007.

- Canedo, A. Ben Abdallah, and M. Sowa, "Queue Register File Optimization Algorithm for QueueCore Processor", Proc. IEEE 19th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2007), pp. 169-176, 2007.

- Canedo, A. Ben Abdallah, and M. Sowa, "An Efficient Code Generation Algorithm for Code Size Reduction using 1-offset P-Code Queue Computation Model", Proc. IFIP International Conference on Embedded and Ubiquitous Computing (EUC07), pp. 196-208, 2007.

- Canedo, A. Ben Abdallah, and M. Sowa, "Compiler Framework for an Embedded 32-bit Queue Processor", Proc. of the International Conference on Convergence Information Technology (ICCIT07), Gyeongju, South Korea, pp. 877-884, 2007.

- 100. Yuki, T.; Canedo, A.; Abderazek, B.A.; Sowa, M., "Novel Addressing Method for Aggregate Types in Queue Processors," Convergence Information Technology, 2007. International Conference on , vol., no., pp.1793,1796, 21-23 Nov. 2007.

- 101.Arquimedes Canedo, Ben Abdallah Abderazek, and Masahiro Sowa, "Queue Compiler Development", IPSJ-SIGPRO, 2007-2-(10).

- 102.Ben Abdallah, T. Yoshinaga, and M. Sowa, "High-Level Modeling and FPGA Prototyping of Produced Order Parallel Queue Processor Core", Journal of supercomputing, Vol. 38, Number 1, pp. 3-15, 2006.

- 103.Ben Abdallah, Sotaro Kawata, and M. Sowa, "Design and Architecture for an Embedded 32-bit QueueCore", Journal of Embedded Computing, Special Issue in embedded single-chip multicore architectures, Vol. 2, No. 2, pp. 191-205, 2006.

- 104.Ben Abdallah, and M. Sowa, "Advanced Power Reduction Techniques in Mobile Computing Systems", ISBN:1-60021-207-7, Nova Science Publishers, 2006.

- 105.Ben Abdallah, T. Yoshinaga, and M. Sowa, "Scalable Core-Based Methodology and Synthesizable Core for Systematic Design Environment in Multicore SoC (MCSoC)", Proc. IEEE 35th International Conference on Parallel Processing Workshops, Aug. 14-18th, pp. 345-352, 2006.

- 106.Ben Abdallah, Masahiro Sowa, Basic Network-on-Chip Interconnection for Future Gigascale MCSoCs Applications: Communication and Computation Orthogonalization, Proc. of the Symposium on Science, Society, and Technology (TJASSST2006), pp. 4-6, 2006/12.

- 107.Musfiquzzaman, A. Ben Abdallah, and M. Sowa, "On the Design of a Dual-Execution Modes Processor: Architecture and Preliminary Evaluation", Frontiers of High Performance Computing and Networking – ISPA 2006 Workshops, Lecture Notes in Computer Science Volume 4331, 2006, pp 37-46.

- 108. Arquimedes Canedo, Ben Abdallah Abderazek, and Masahiro Sowa, "A GCC-based Compiler for the Queue Register Processor (QRP-GCC)", The International Workshop on Modern Science and Technology 2006.

- 109.T. Viet, T. Toshinaga , A. Ben Abdallah, and M. Sowa, "Construction of Hybrid MPI-OpenMP Solutions for SMP Clusters", IPSJ transactions on Advanced Computing Systems, Vol.46, pp.25-37, Jan. 2005.

- 110.M. Sowa, A. Ben Abdallah, and T. Yoshinaga, "Processor Architecture Based on Produced Order Computation Model", Journal of Supercomputing, Vol. 32, No. 3, pp. 217-229, June 2005.

- 111.Ben Abdallah, M. Arsenji, S. Shigeta, T. Yoshinaga, and M. Sowa, "Modular Design Structure and High-Level Prototyping for Novel Embedded Processor Core", Proc. of International Conference on Embedded and Ubiquitous Computing (EUC2005), LNCS Vol.3824, pp. 340-349, 2005.

- 112.M. Akanda, A. Ben Abdallah, S. Kawata, and M. Sowa, "An Efficient Dynamic Switching Mechanism (DSM) for Hybrid Processor Architecture", Proc. of International Conference on Embedded and Ubiquitous Computing (EUC2005), LNCS Vol.3824, pp. 77-86, Dec. 2005.

- 113.Markovskij, A. Ben Abdallah, S. Kawata, and M. Sowa, "Architecture of Produced-order Parallel Queue Processor: Preliminary Evaluation", Proc. of the 38th International Symposium on Microarchitecture (MICRO-38), Nov. 2005.

- 114.Ben Abdallah, T. Yoshinaga, and M. Sowa, "Rapid FPGA Prototyping of a Queue Processor Core for Embedded Computing", Proc. of 67th Conf. of Information Processing Society of Japan, March 2~4, 2005.

- 115.Ta Quo Viet, T. Yoshoinaga, and A Ben Abdallah, "Performance Enhancement for Matrix Multiplication on an SMP PC Cluster", Summer United Workshops on Parallel, Distributed and Cooperative Processing, August 2005.

- 116.Ben Abdallah, Markov Arsenji, S. Shigeta, T. Yoshinaga, and M. Sowa, "Queue Processor for Novel Queue Computing Paradigm Based on Produced Order Scheme", Proc. IEEE of the 7th High Performance Computing and Grid in Asia Pacific Region (HPCAsia2004), pp. 169-177, July 2004.

- 117.Shigeta, L.-Q. Wang, N. Yagishita, A. Ben Abdallah, T. Yoshinaga, and M. Sowa, "QJava: Integrate Queue Computational Model into Java", Proc. of the Joint Japan-Tunisia Workshop on Computer Systems and Information Technology (JT-CSIT'04), July 2004.

- 118.Markovskij, M. Sowa, A. Ben Abdallah, S. Shigeta, and T. Yoshinaga, 'Design of Producer-Order Parallel Queue Processor Architecture'', Proc. of International Workshop on Modern Science and Technology (IWMST 2004), September 2-3, 2004.

- 119.M. Akanda, A. Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "High performance Hybrid Processor Architecture with Efficient Hardware Usability", Proc. of International workshop on Modern Science and Technology (IWMST 2004), September 2-3, 2004.

- 120.H. Sasaki, Y. Okumura, A. Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "Theoretical Evaluation of Simultaneous Multi threading Parallel Queue Processor Architecture", Proc. International Conference on Circuits/Systems, Computers and Communications, July 2004.

- 121.Ben Abdallah, M. Arsenji, K. Kiuchi, M. Akanda, S. Shigeta, T. Yoshinaga, and M. Sowa, "PQPpfB: Parallel Queue Processor Architecture in Verilog-HDL", Proc. of 66th Information Processing Society of Japan, pp. 3F-4, March 2004.

- 122. T. Viet, T. Toshinga, A. Ben Abdallah, and M. Sowa, "Optimization for Hybrid MPI-OpenMP Programs on a Cluster of SMPs", SACSIS 2004.

- 123.Musfiquzzaman, A. Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "Queue Computation Mechanism For Parallel Execution in Parallel Queue Processor", Proc. of Information Processing Society of Japan, Vol. 60, pp. 3F-4, 2004. Canedo Arquimedes<sup>†</sup>, Abderazek Ben, Yoshinaga Tsutomu, Sowa Masahiro, "A General Purpose Assembler for Queue Computers", Proc. of IPSJ Symposium, 2004, [paper.pdf]

- 124.Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "On the Design of a Register Queue Based Processor Architecture (FaRM-rq)", Lecture Note on Computer Scinece LNCS 2745, International Symposium of Parallel and Distributed Processing and Applications (ISPA 2003), pp.248-262, July 2003.

- 125.L. Q. Wang, A. Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "QJAVAC: Queue-Java Compiler Design for High Parallelism Queue Java Bytecode", Proc. of International Technical Conference in Circuits/Systems, Computers and Communications (ITC-CSCC2003), pp. 900-903, July 2003.

- 126. Tao. Q. Viet, T. Yoshinaga, A. Ben Abdallah, and M. Sowa, "A Hybrid MPI-OpenMP Solution for a Linear System on a Cluster of SMPP", SACSIS03, pp.299-306, 2003.

- 127.L. Wang, A. Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "QJAVAC: Queue-Java Compiler Design for High Parallelism Queue Java", Proc. of IEICE Technical conference, 2003.

- 128.T. Q. Viet, T. Yoshinaga, A. Ben Abdallah, and M. Sowa, "A Hybrid MPI-OpenMP Solution for a Linear System on a Cluster of SMPs", Proc. of Symposium on Advanced Computing Systems and Infrastructures, pp.299-306, 2003.

- 129.Ben Abdallah, "Dynamic Instructions Issue Algorithm and a Queue Execution Model Toward the Design of Hybrid Processor Architecture", Ph.D. thesis, Graduate School of Information Systems, the Univ. of Electro-Communications at Tokyo, March 2002.

- 130.Ben Abdallah, S. Shigeta, T. Yoshinaga, and M. Sowa, "Complexity Analysis of a Functional Assignment Register Microprocessor", Proc. of the Int. Workshop on Modern Science and Technology (IWMST02), pp.116-123, Sep. 2002.

- 131.Ben Abdallah, K. Nikolova, and M. Sowa, "FARM-Queue Mode: On a Practical Queue Execution Model", Proc. of the Int. Conf. on Circuits and Systems, Computers and Communications, pp.939-944, July 2001.

- 132.Kiriuka Nikolova, A. Ben Abdallah, and M. Sowa, "Dynamical Critical Path Parallelism-Independent Scheduling Algorithm for Distributed Computing Systems", Proc. of the International Technical Conference on Circuits and Systems, Computers and Communications, pp. 929-934, July 2001.

- 133.Ben Abdallah, Mudar Sarem, and M. Sowa, Dynamic Fast Issue Mechanism (DFI) for Dynamic Scheduled Processors, IEICE transactions on Fundamental of Electronics, Communications and computer Science, Vol. E83-A No.12 pp.2417-2425, Dec. 2000.

- 134.Ben Abdallah, Mudar Sarem, and M. Sowa, "Dynamic Fast Issue Mechanism (DFI) for Dynamic Scheduled Processors", IEICE transactions on Fundamental of Electronics, Communications and computer Science, Vol. E83-A No.12 pp.2417-2425, Dec. 2000.

- 135.Ben Abdallah, and M. Sowa, "DRA: Dynamic Register Allocator Mechanism for FaRM Microprocessor", Proc. of the 3rd International Workshop on Advanced Parallel Processing Technologies (APPT'99), pp.131-136, October 1999.